# **ARM Based Systems**

Géza Lőre

Research Engineer, ARM Ltd Geza.Lore@arm.com

# Agenda

- Introduction to ARM Ltd

- ARM Architecture / Programmers Model

- Microarchitectures

- AMBA

- Example ARM based SoC

# ARM Ltd

- Founded in 1990

- Spun out of Acorn Computers

- Primary product: RISC processor cores

- ARM is an Intellectual Property (IP) company

- We do not fabricate or sell silicon

- We license technology to our partners

- Our partners design and fabricate products, which they sell to their customers

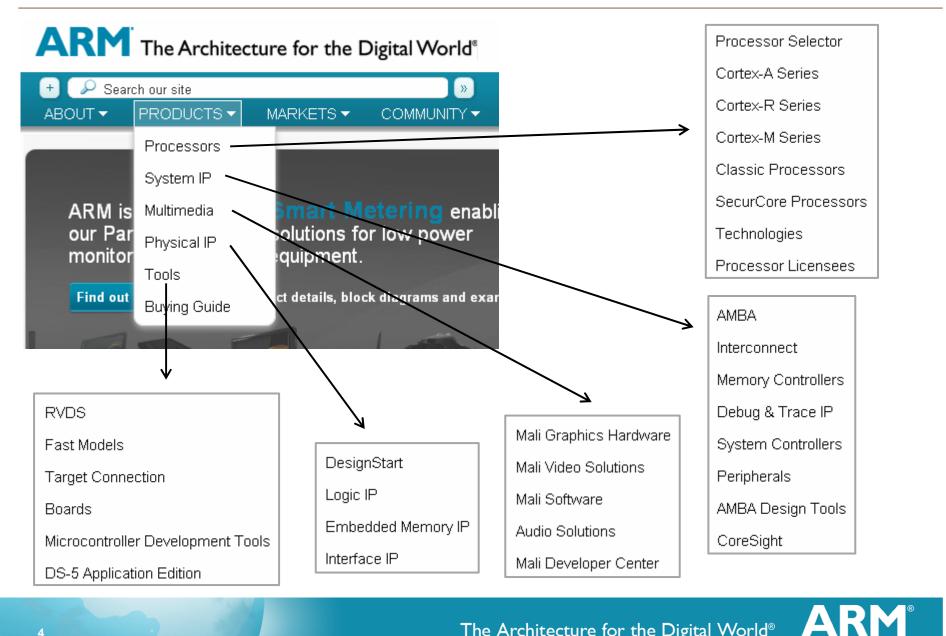

- Develops technologies to assist with the design-in of the ARM architecture

- Software tools, application software

- Development boards, debug hardware

- Bus architectures, peripherals, etc.

# **ARM's Activities**

## **ARM Connected Community – 550+**

The Architecture for the Digital World®

### **Applications**

The Architecture for the Digital World®

# Agenda

- Introduction to ARM Ltd

- ARM Architecture / Programmers Model

- Microarchitectures

- AMBA

- Example ARM based SoC

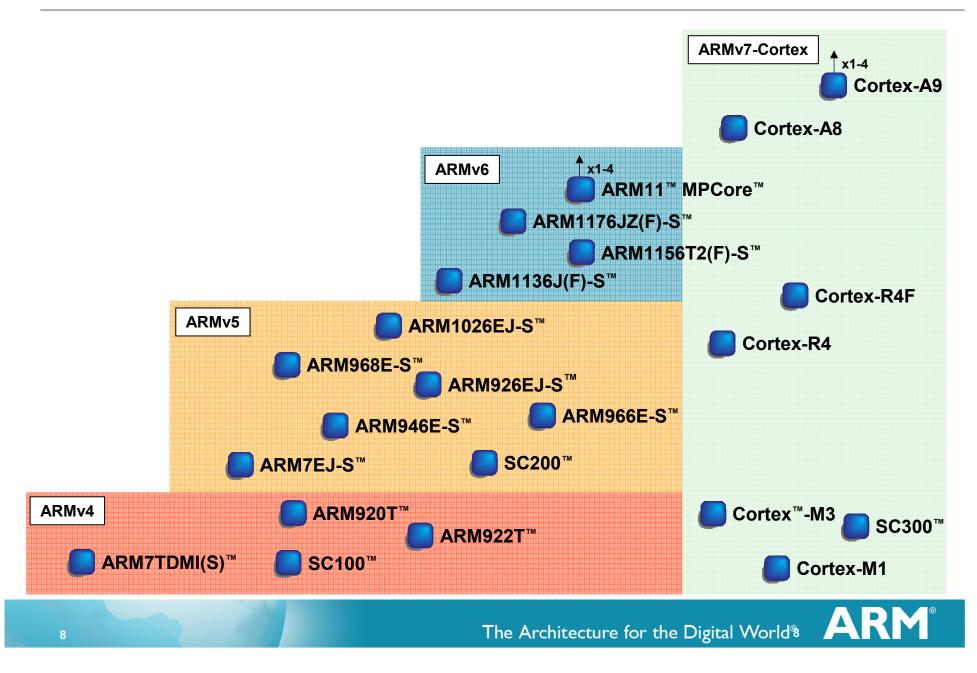

#### **Architecture Versions**

# **Data Sizes and Instruction Sets**

- The ARM is a 32-bit Load/Store architecture

- Registers are 32 bit wide

- Operations carried out on registers

- Memory accessed only with Load and Store operations

- Most ARM's implement two instruction sets

- 32-bit ARM Instruction Set

- 16-bit Thumb Instruction Set

- Multiple optional extensions are available

- Jazelle execute Java bytecode in hardware

- NEON Advanced SIMD engine

- TrustZone security extensions

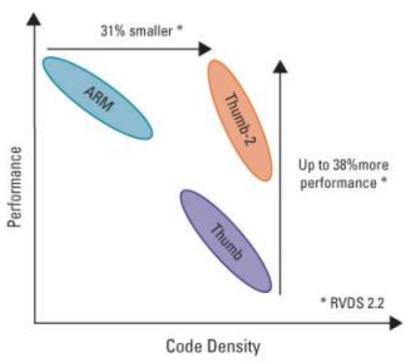

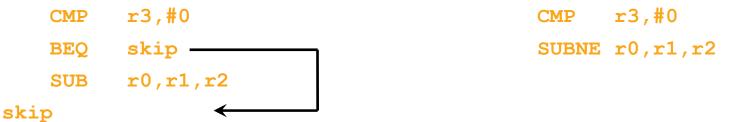

# **ARM vs Thumb vs Thumb-2**

- ARM Instruction set

- High performance

- All instructions are 32 bit

- All instructions can be conditional

- Thumb

- Re-encoded subset of the ARM ISA

- All instructions are 16 bit

- Restricted functionality

#### Thumb-2

- Extension of Thumb

- 16 and 32 bit instructions mixed

- Full functionality available

Instruction sets can be mixed in the same program: Interworking

The Architecture for the Digital World®

## Intsruction set details

#### Conditional execution of ARM instructions

Barrel shifter in the data path

ADD r1,r2,r2,LSL #3 ; r1 = 9\*r2 SUB r4,r4,r5,LSR #2 ; r4 = r4 - 0.25\*r5 RSB r3,r3,r3,LSL #2 ; r3 = 3\*r3

Check the appropriate ARM Architecture Reference Manual (ARM ARM)

http://infocenter.arm.com/

The Architecture for the Digital World<sup>®</sup>

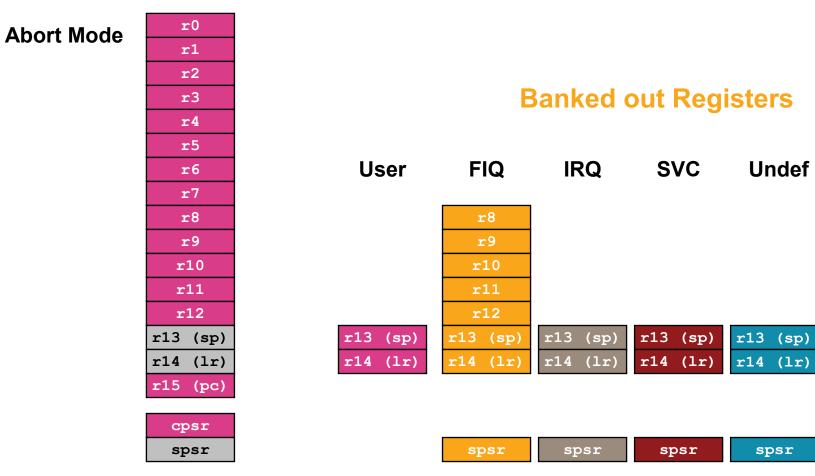

# **Processor Modes (Classic)**

- The ARM has seven basic operating modes:

- User : unprivileged mode under which most tasks run

- **FIQ** : entered when a high priority (fast) interrupt is raised

- IRQ : entered when a low priority (normal) interrupt is raised

- Supervisor : entered on reset and when a Software Interrupt instruction is executed

- Abort : used to handle memory access violations

- Undef : used to handle undefined instructions

- System : privileged mode using the same registers as user mode

## **The ARM Register Set**

#### **Current Visible Registers**

# **Exception Handling**

- When an exception occurs, the ARM:

- Copies CPSR into SPSR\_<mode>

- Sets appropriate CPSR bits

- Change to ARM state

- Change to exception mode

- Disable interrupts (if appropriate)

- Stores the return address in LR\_<mode>

- Sets PC to vector address

- To return, exception handler needs to: 0x04

- Restore CPSR from SPSR\_<mode>

- Restore PC from LR\_<mode>

This can only be done in ARM state.

| 0x1C | FIQ                   |

|------|-----------------------|

| 0x18 | IRQ                   |

| 0x14 | (Reserved)            |

| 0x10 | Data Abort            |

| 0x0C | Prefetch Abort        |

| 0x08 | Software Interrupt    |

| 0x04 | Undefined Instruction |

| 0x00 | Reset                 |

**Vector Table**

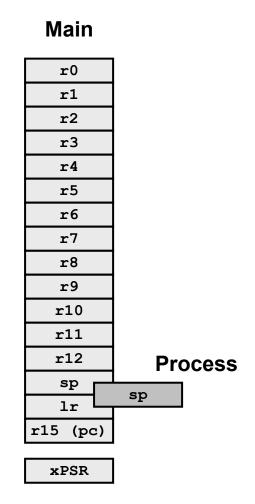

# **Cortex-M Programmer's Model**

- ARMv7-M (Cortex-M class processors) have a different programmer's model

- Fully programmable in C

- Stack-based exception model

- Only two processor modes

- Thread Mode for User tasks

- Handler Mode for OS tasks and exceptions

- Vector table contains addresses

# Agenda

- Introduction to ARM Ltd

- ARM Architecture / Programmers Model

- Microarchitectures

- AMBA

- Example ARM based SoC

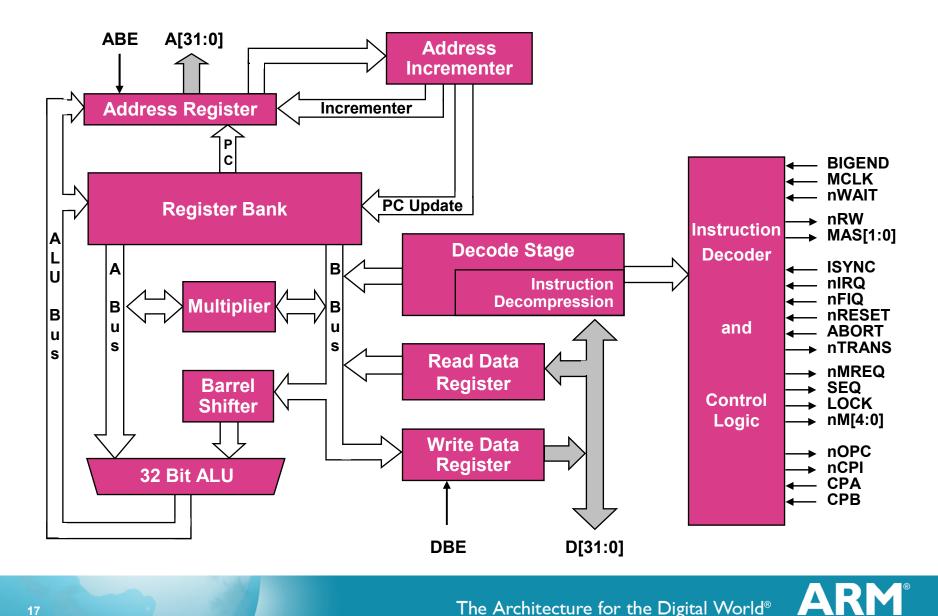

## The ARM7TDMI Core (ARMv4)

The Architecture for the Digital World®

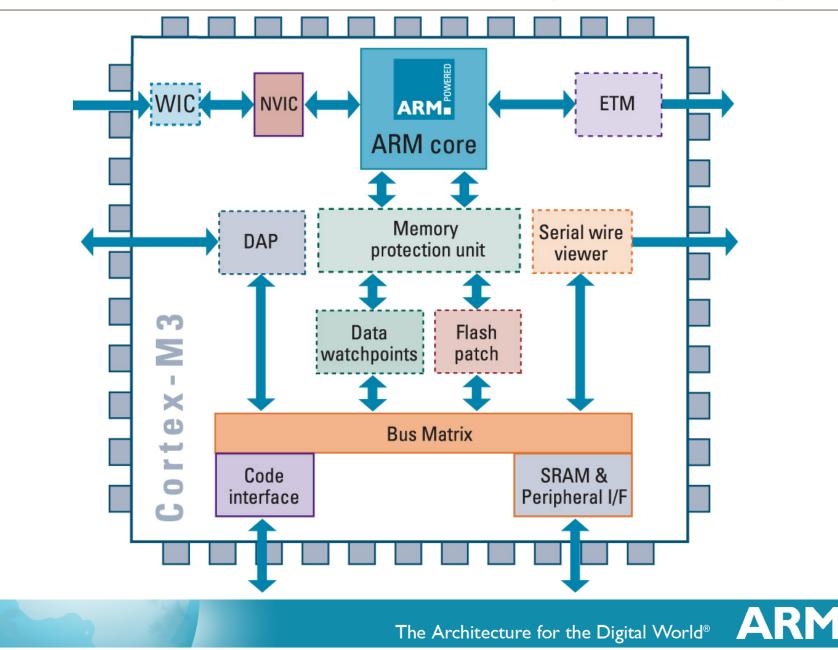

#### The Cortex-M3 processor (ARMv7-M)

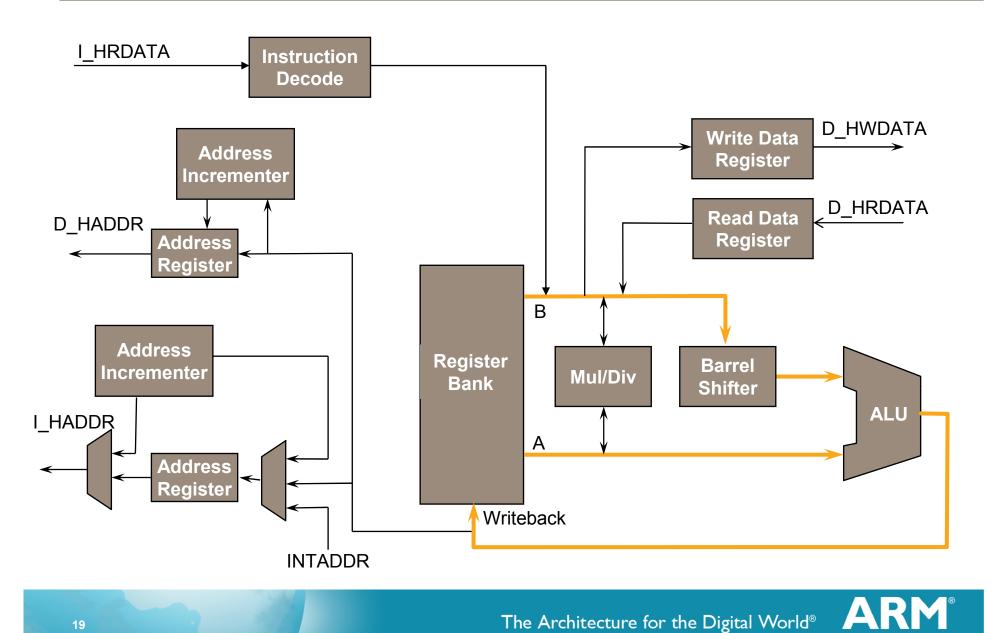

### **Cortex-M3 Datapath**

The Architecture for the Digital World®

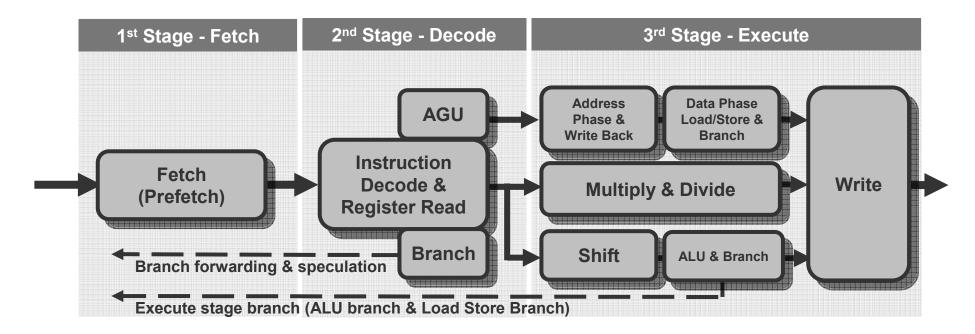

# **Cortex-M3 Pipeline**

- Cortex-M3 has 3-stage fetch-decode-execute pipeline

- Similar to ARM7

- But Cortex-M3 does more in each stage to increase overall performance

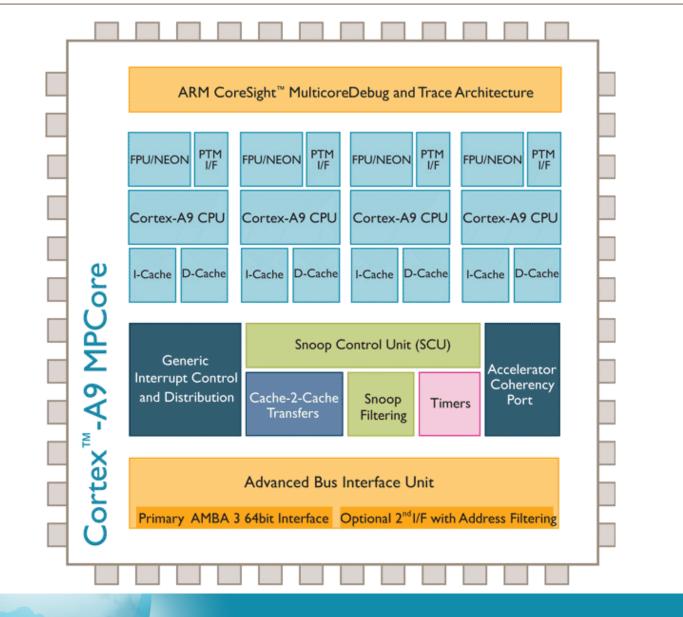

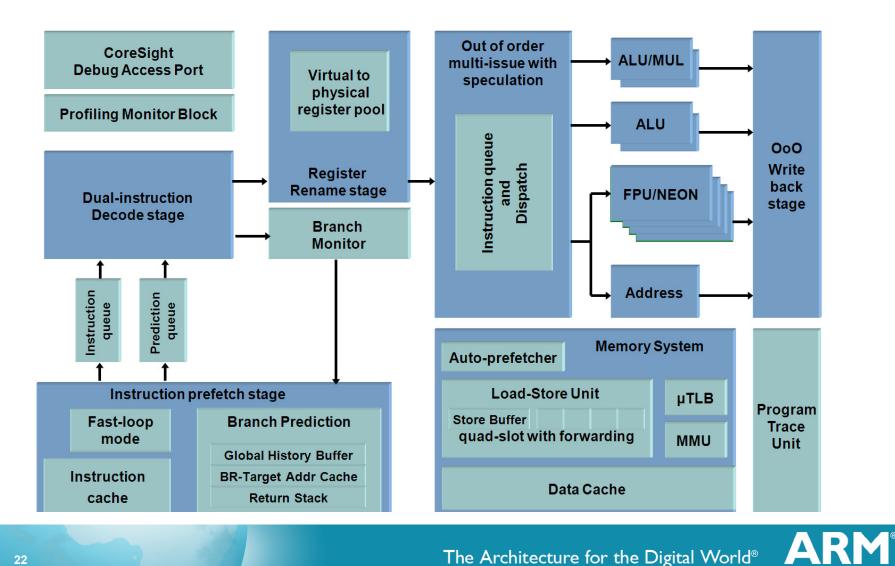

## The other end: Cortex-A9 (ARMv7-A)

The Architecture for the Digital World®

## **Cortex-A9** Pipeline

8-stage, Out-of-Order, Multi-issue superscalar

The Architecture for the Digital World®

# Agenda

- Introduction to ARM Ltd

- ARM Architecture / Programmers Model

- Microarchitectures

- AMBA

- Example ARM based SoC

# AMBA

- AMBA is an open standard owned and maintained by ARM

- AMBA 3 contains 4 main interface specifications:

- APB Advanced Peripheral Bus

- AHB Advanced High-performance Bus

- AXI Advanced eXtensible interface

- ATB Advanced Trace Bus

- Newest version: AMBA 4 since March 2010

- Some modifications to AXI

- Introducing

- AXI Stream

- AXI-Lite

# AXI 3

- Original version of AXI, defined in AMBA 3

- Used by current IP

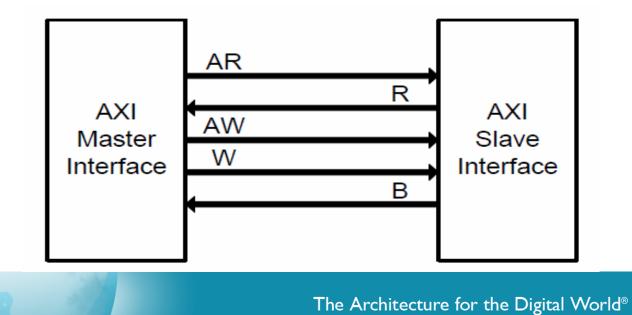

- AXI is a simple *point-to-point* link

- 5 independent channels

- Each channel is a set of signals going in the same direction

# **AXI channels**

#### The 5 channels are

- AR: Read Address channel

- R: Read Data channel

- AW: Write Address channel

- W: Write Data channel

- B: Write Response channel

- Address channels carry control information and 32 bit addresses

- Data channels carry powers of 2 wide data (between 8-1024) together with some control signals

- Each channel contains

- ID signals

- VALID and READY handshake signals

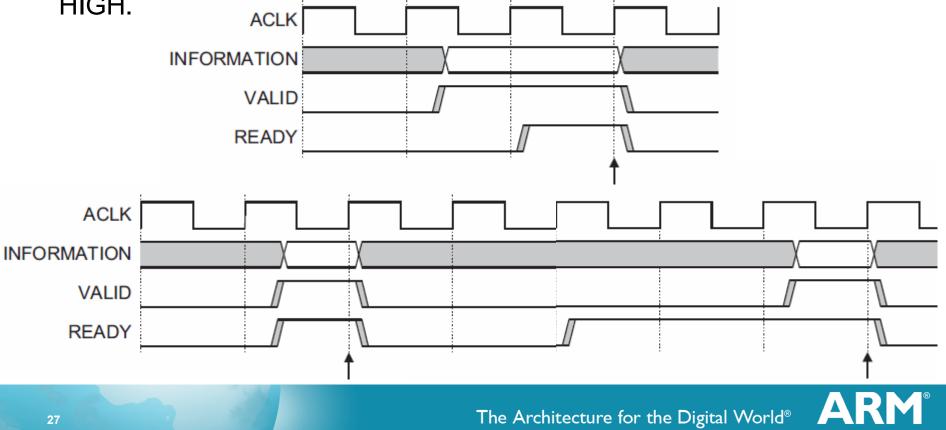

# AXI handshake

- The source generates the VALID signal to indicate when the information is available

- The destination generates the **READY** signal to indicate that it accepts the information

- Transfer occurs only when both the VALID and READY signals are HIGH.

# **AXI transactions**

- Parts of a transaction are identified by the transaction ID

- Read transaction

- Master sends Read Address on AR channel

- Slave sends Read Data and Response on R channel

- Write transaction

- Master sends Write Address on AW channel

- Master sends Write Data on W channel

- Slave sends Write Response on B channel

- Transactions can have different (among others)

- Burst length (1-16 beat)

- Burst type (FIXED, INCR, WRAP)

- Protection properties

- AXI supports

- Multiple outstanding transactions

- Out of order transaction completition

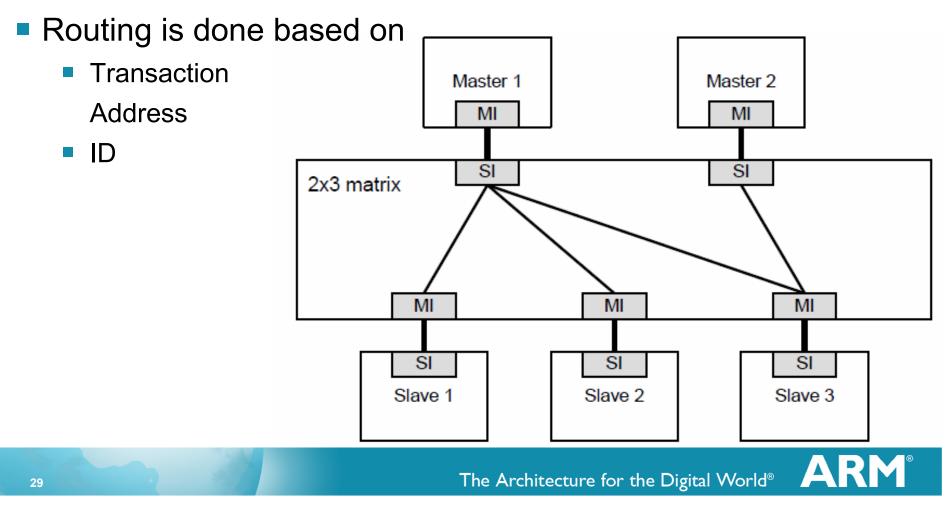

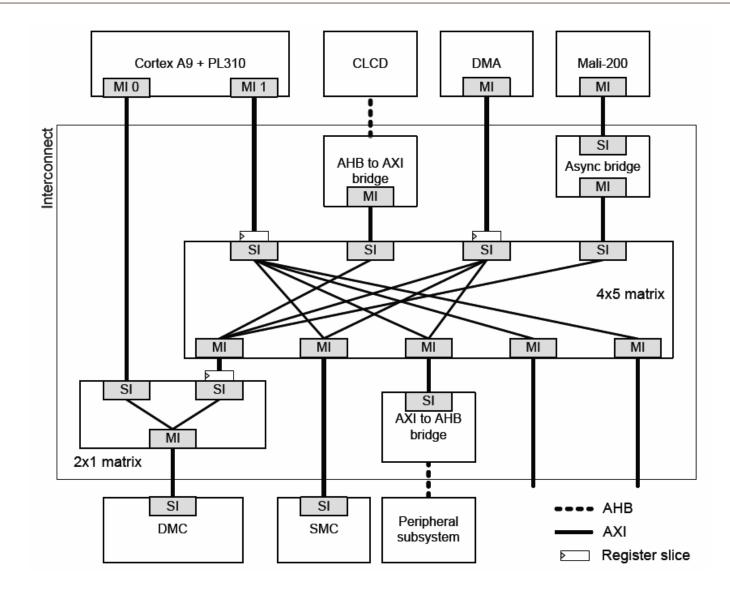

# **AXI** based interconnects

- AXI is a point-to-point link

- In practice, we build cross bar switches (or matrices) to route transactions between multiple masters and slaves

# Agenda

- Introduction to ARM Ltd

- ARM Architecture / Programmers Model

- Microarchitectures

- AMBA

- Example ARM based SoC

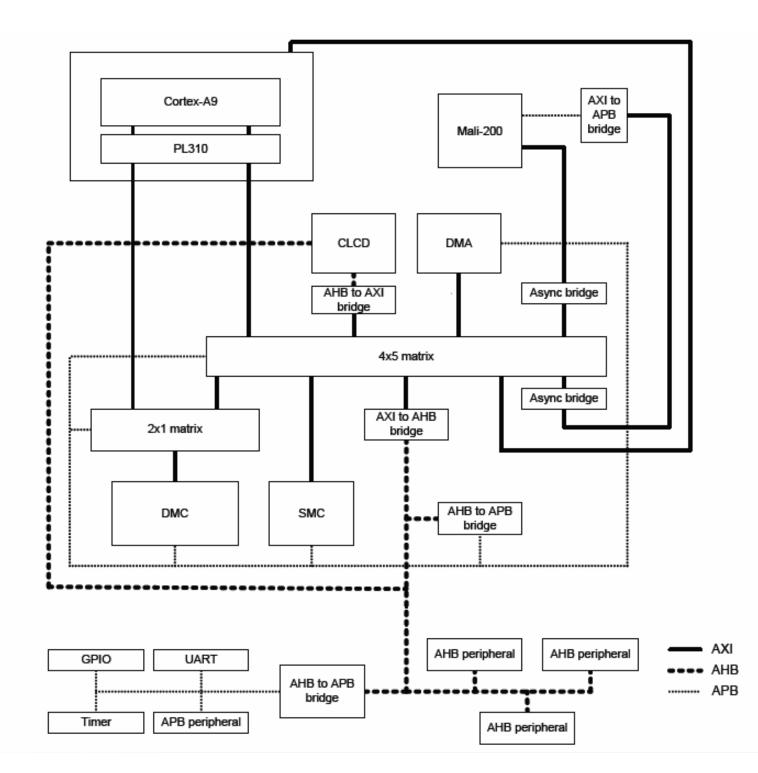

#### **Example ARM based system**

The Architecture for the Digital World®

ARM

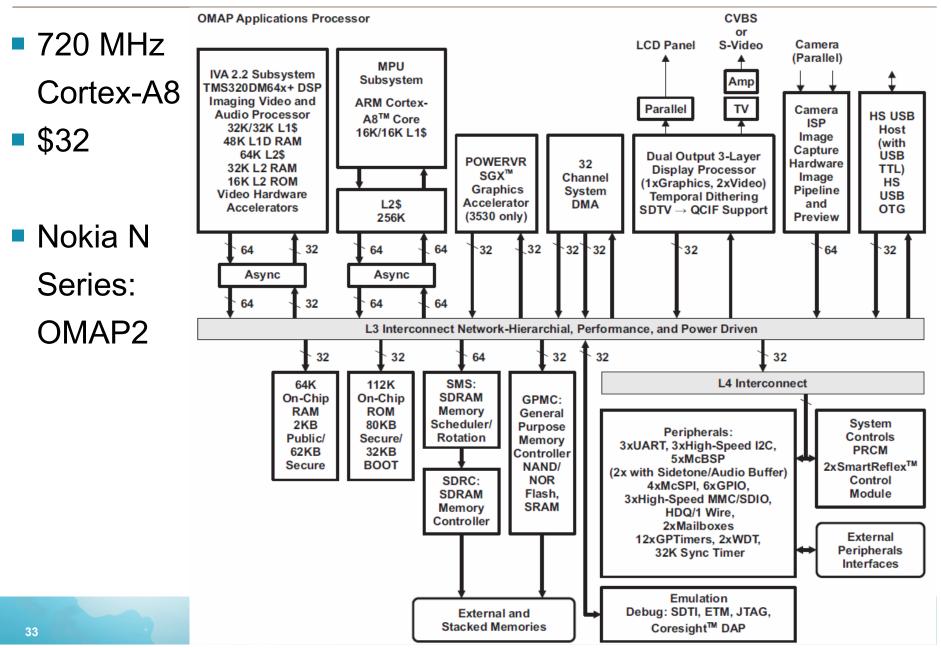

# A real SoC: TI OMAP3530

## Back to the low end

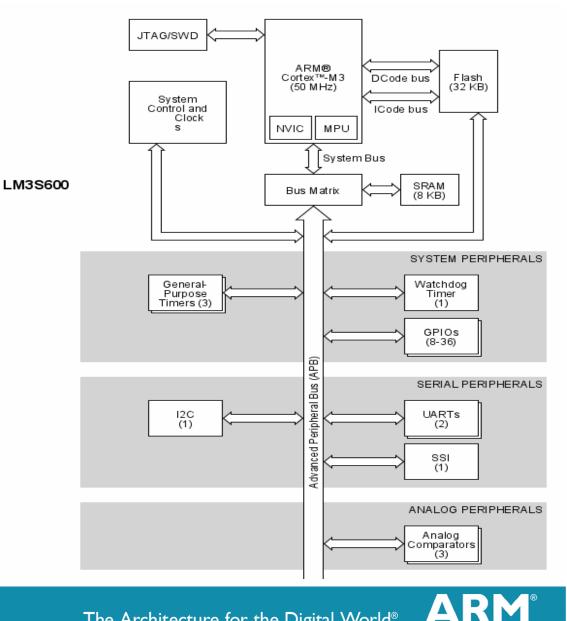

- Stellaris® LM3S600 Microcontroller

- 50 MHz Cortex-M3

**\$**2

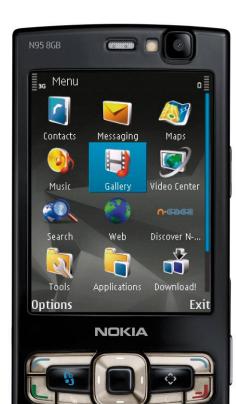

# Putting it all together: Nokia N95

#### OMAP<sup>™</sup> 2420 Applications Processor ARM1136<sup>™</sup> processor-based

SoC, developed using Magma ® Blast® family and winner of 2005 INSIGHT Award for 'Most

Innovative SoC'

Symbian OS<sup>™</sup> v9.2 Operating System supporting ARM processor-based mobile devices, developed using ARM® RealView® Compilation S60<sup>™</sup> 3<sup>rd</sup> Edition S60 Platform supporting ARM processor-based mobile devices

Mobiclip<sup>™</sup> Video Codec Software video codec for ARM processor-based mobile devices

ST WLAN Solution Ultra-low power 802.11b/g WLAN chip with ARM9<sup>™</sup> processor-based MAC

#### Connect. Collaborate. Create.

The Architecture for the Digital World®

#### **Conclusions** -

¥

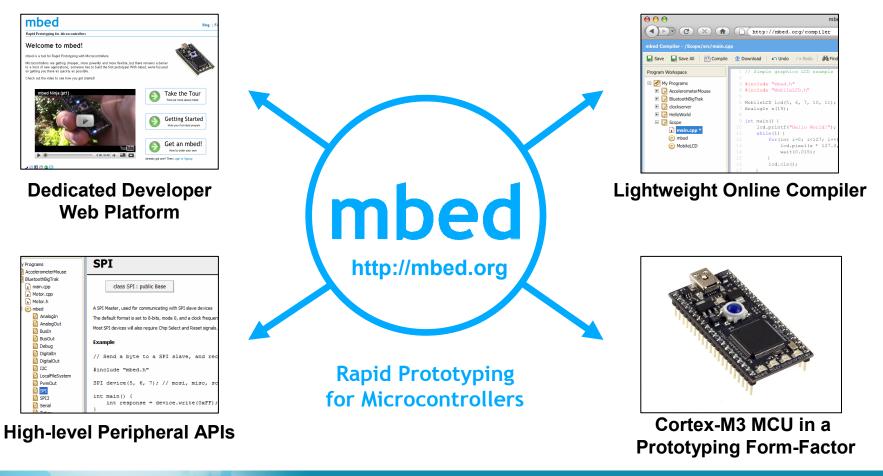

# If you want to play 🙂

#### Getting Started and Rapid Prototyping with ARM MCUs

Complete Targeted Hardware, Software and Web 2.0 Platform