# Digital design laboratory 1

- The goal of the laboratory is to provide an opportunity to use and test the theoretical concepts you studied on lecture on a real hardware.

- For this purpose, we are going to use an FPGA board

- FPGA stands for Field-programmable gate array

- Fundamentally, the FPGA consists of a large number of logic blocks, and the way these blocks are wired together can be defined by the user

- In addition, the functionality of the logic blocks can be defined also

- For example, a logic block can be used as a memory component, or it can be used to do mathematical operations (e.g. adding two numbers).

- FPGA-s can be configured using a hardware description language (HDL).

- These languages have their own syntax, but it's often quite similar to traditional computer programming languages.

- However, there is one very important difference between computer programming languages and hardware description languages.

- In CPLs, the instructions are executed **sequentially**, one-by-one.

- In HDLs, the instructions are executed parallelly, more at the same time.

- Let's demonstrate this with a simple example.

• Take a look at the following C code:

```

int a = 0, b = 0;

while (1) {

a = a + 1;

b = a + 1;

}

```

• First the memory is allocated for a and b, then the value of a is updated with a+1, then b's value is set to a+1.

- After the first cycle the the value of a will be 1 and the value of b will be 2.

- In the nth cycle a will be n and b will be n+1.

- The assignment of a always precedes the assignment of b, so these two variables will never have the same value at the end of the cycles.

• Take a look at the following Verilog code. Do not worry about the syntax (it is not important now), this is the Verilog version of the above C code.

```

reg [31:0] a; // 32 bit registers for storing

reg [31:0] b; // integer data

always @ (posedge clk) // some condition, not important

begin

```

a <= a + 1; b <= a + 1;

#### end

Since Verilog evaluates the assignment simultaneously, a and b registers will always have the same value.

- The ISE Design Suite 14.6 software will be used on the laboratories to design and implement digital circuits.

- To launch the application, click on the icon on the desktop:

- Or launch it from the Start menu:

- Start -> All Programs -> Xilinx Design Tools -> ISE Design Suite 14.6 -> ISE Design Tools -> Project Navigator

- After the navigator has started, it is time to create your first project.

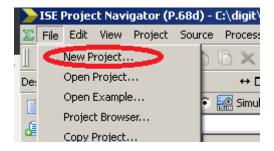

- Select File, then New Project...

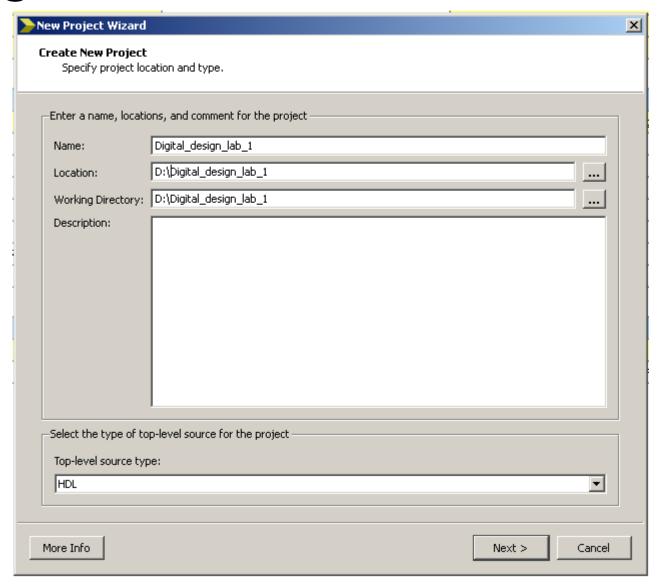

- The New Project Wizard appears. Next slide shows how to fill the textboxes.

- General rule: always work on the D: drive!

- Name: Digital\_design\_lab\_1

- Locaton and Working Directory:D:\Digital\_design\_lab\_1

- Description: this can be empty

- Top-level source type: HDL

- If everything is set, press Next.

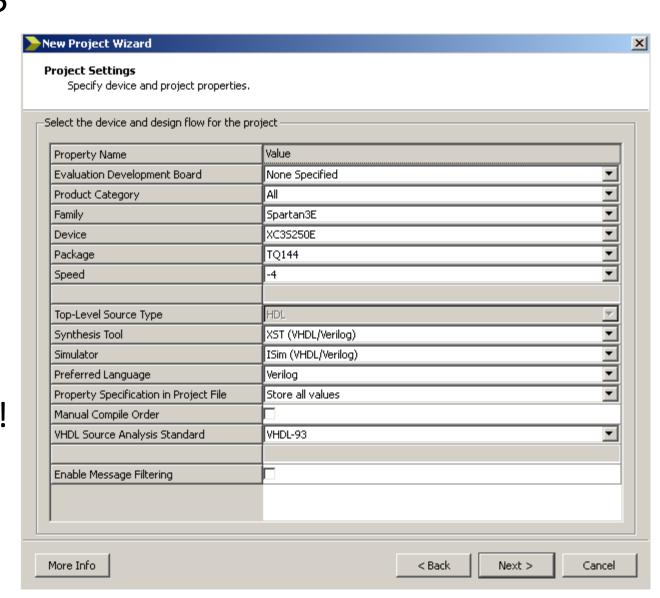

• Set the following:

Family: Spartan3E

Device: XC3S250E

Package: TQ144

• Speed: -4

- Do not modify the other settings!

- Press Next

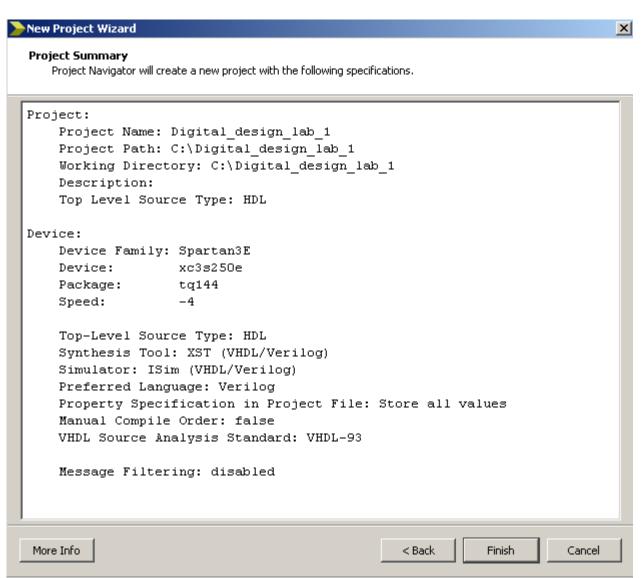

- The following window appears:

- Just press Finish

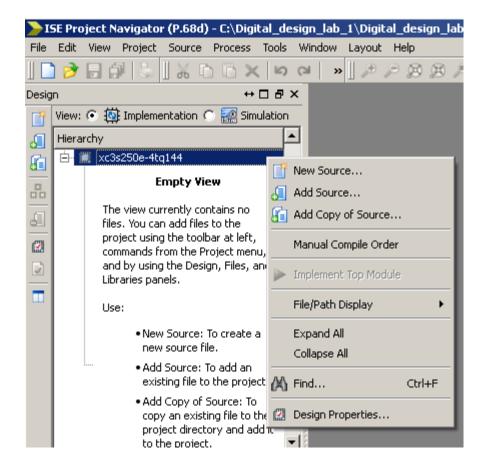

The following screen appears:

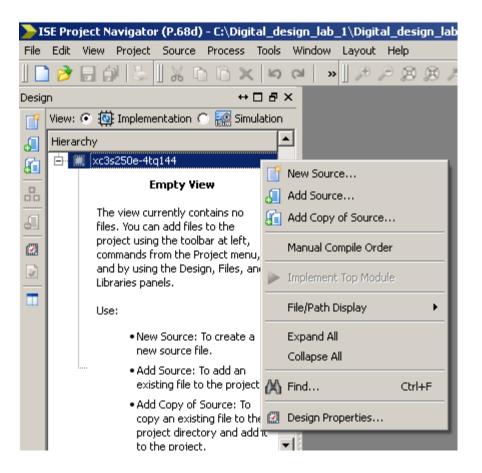

• To get started, right click on the xc3s250e-4tq144 label, and select New source... from the menu.

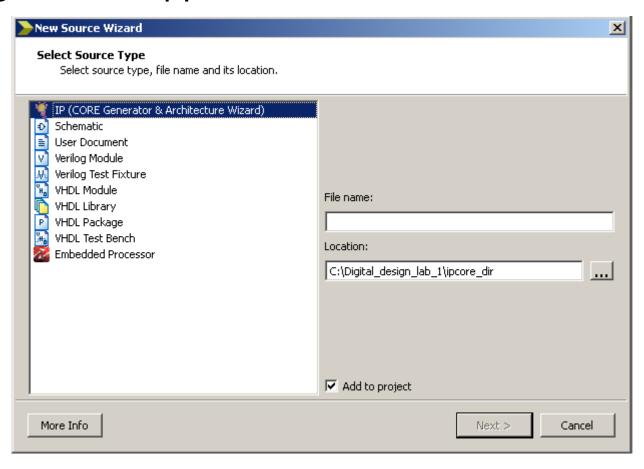

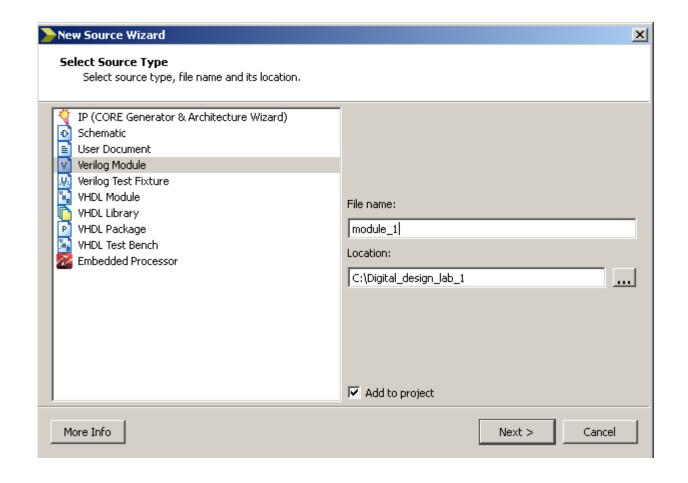

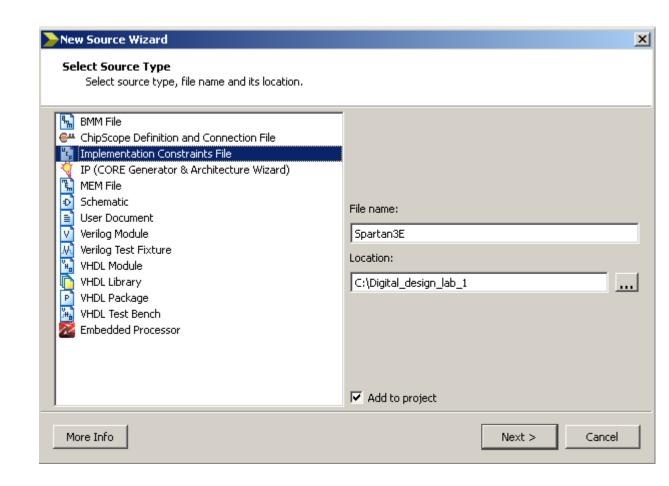

The following window appears:

- Select Verilog Module

- File name: module\_1

- Make sure the 'Add to project' checkbox is selected

- Do not modify the Location

- Press Next

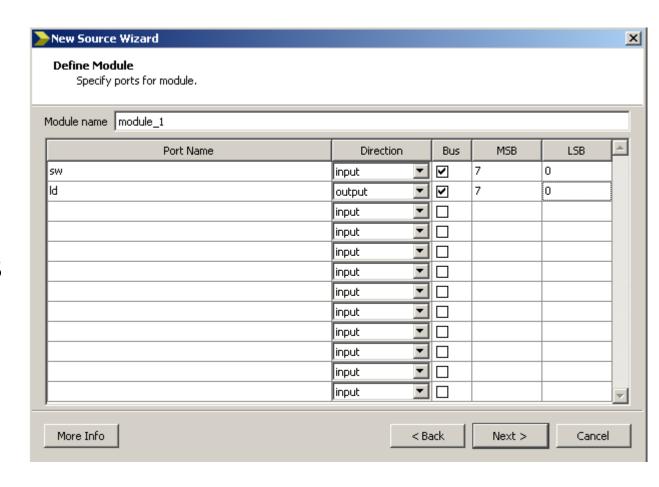

- The New Source Wizard appears:

- Add to new ports: sw, ld

- Set the direction of sw to input

- Set the direction of ld to output

- Check the Bus checkbox for both ports

- Set the value of the MSB to 7, and the value of the LSB to 0 for both ports

- Press the Next button

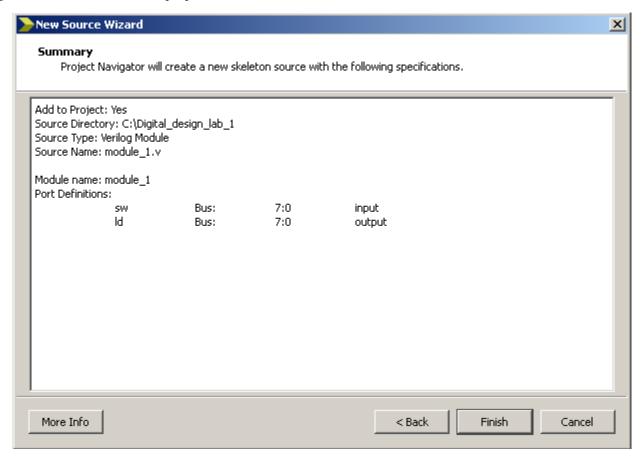

- The following window appears:

- Press Finish

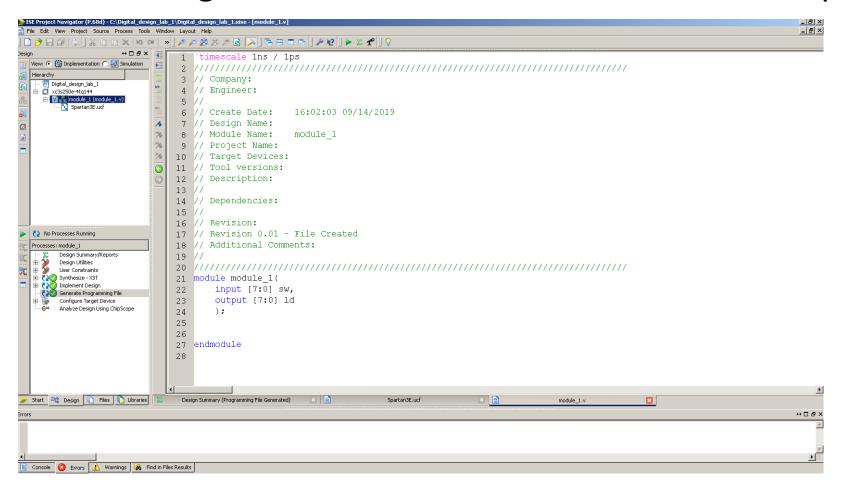

• The ISE software generates the editable source file for the project:

Now you can create your first "Hello World" module.

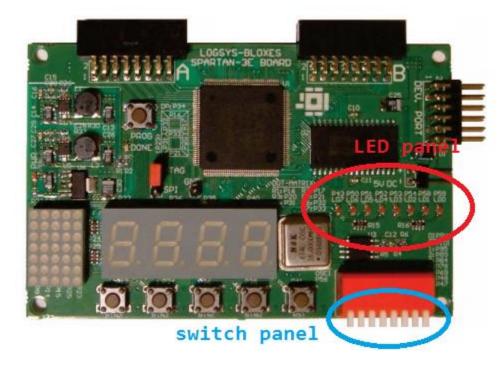

• After you have finished with the code, you can test your module on

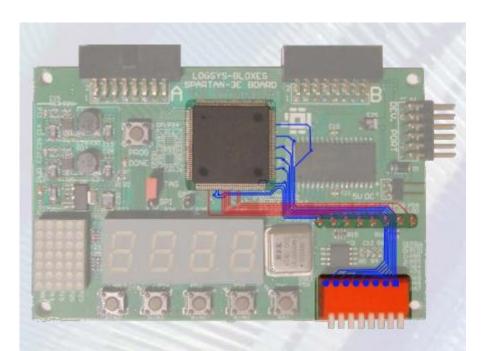

an FPGA board:

The FPGA itself is the black, square shaped device in the middle of the board

• In this first design, you are going to control the LED panel of the FPGA using the switches: if a switch is turned on, the corresponding LED will light up.

- We need to define a connection between the LEDs and the switches using Verilog. The aim is to connect them one-by-one.

- The LEDs are connected to the outputs (red wires) of the FPGA, while the switches are connected to the inputs (blue wires).

- In the implementation, we will connect these inputs and outputs "inside" the FPGA

To do so, add the following line to your module:

```

module module 1(

input [7:0] sw,

output [7:0] ld

23

);

24

25

assign ld = sw;

26

27

endmodule

20

```

• Don't forget to press the save button

- As a last step, you have to define the connection between your own port names (ld and sw), and the port pins of the FPGA.

- Take a close look at the LEDs of the board. You can see the matching of the LEDs and the corresponding ports of the FPGA. For example, LD0 is connected to P59, LD1 is connected to P58, and so on.

- The name of the leds in our module is ld, which is an 8 bit output. So we have to define that ld[0] is connected to port P59, ld[1] is connected to port P58, and the same for the rest of the leds (up to ld[7], the 8<sup>th</sup> led).

- The same definition has to be done also for the switches. Check the lower right corner of the board.

- You can see the matchings between the switches and the input ports: sw[0] is connected to port P101, sw[1] connects to P95, and so on.

- We need to provide this information somewhere in our project before we generate the programming file and download it to the board.

- For this purpose, we have to add a .UCF file (User Constraints File) to the project.

Right click on "xc3s250e-4tq144" in the top left corner of the ISE window, and select New Source.

- In the next window, select Implementation Constraints File

- File name: Spartan3E

- Do not edit the Location

- Make sure the Add to project checkbox is set

- Press Next

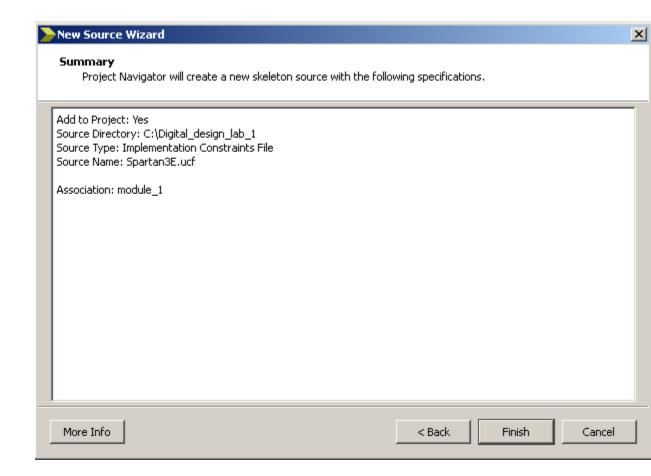

• On the next window, press Finish

- Add the following lines to the UCF file:

- Note: some of the port names after LOC were replaced with question marks.

- Check the board and define the correct missing ports!

- Don't forget to press the save button.

```

b 1\Digital design lab 1.xise-[Spartan3E.ucf]

idow Layout Help

» | 🎤 🔑 🙉 🙉 🥕 🗟 | 🔼 | 🖶 🖽 🖽 🕒 | 🎤 🎌 | | 🕨 🗵 📌 | | 🗸

"sw<7>"

LOC = "P48";

LOC = "P69";

LOC = "????";

LOC = "P84";

LOC = "P89";

LOC = "????";

LOC = "P101";

# 8 LEDs, from the left to the right

"ld<6>"

"ld<5>"

LOC = "????";

"ld<4>"

LOC = "P52";

LOC = "P54";

LOC = "P58";

LOC = "????";

NET "ld<0>"

```

- Now you are ready to generate the so-called programming file

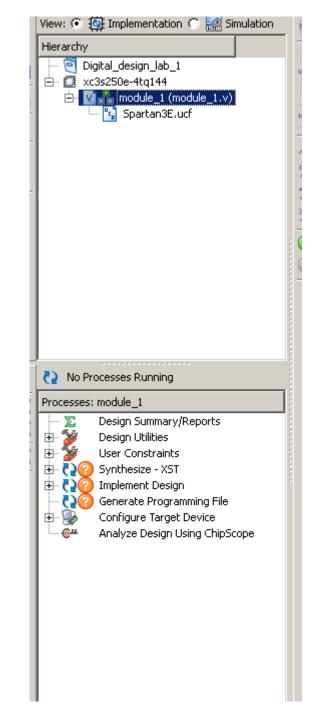

- To do so, left click on module\_1 in the top left corner of the ISE

- On the lower side, the following options appear:

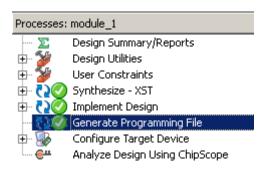

- Right click on Generate programming file, and select Run in the pop up menu.

• If everything was OK, you should see 3 check marks:

• Check your working directory, you should see a new file named "module 1.bit".

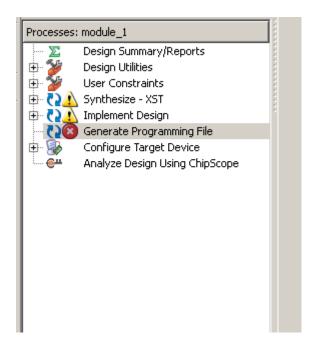

However, if you see anything but the 3 check marks, ask for assistance:

- Before uploading the generated programming file, the board needs some setup.

- First of all, connect the JTAG connector to the board. The labels (TD0, TCK, CLK, MOSI, I/OREF and 5V) should be the oriented the same way as on the following picture, otherwise you might harm the device!

- Connect the USB cable to the JTAG connector.

- Launch the Logsys GUI application

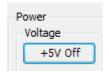

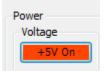

Press the +5V Off button

• After pressing it, it turns into red:

• Select the JTAG download checkbox under Configuration:

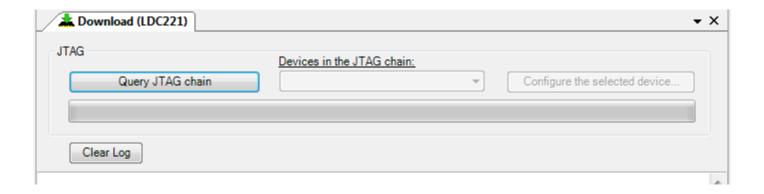

• The following options appear on the right side of the screen:

- Press the Query JTAG chain button, the "Configure the selected device" button becomes active on the right.

- Press it, and browse the "module\_1.bit" file from your working directory.

- After selecting the file, press Open

- After the programming is complete (green status bar), you can try turning the LEDs on and off by flipping the switches.

- Try to set the following decimal and hexadecimal number assuming LD7, LD6, ..., LD0 represent 2<sup>7</sup>, 2<sup>6</sup>, ..., 2<sup>0</sup>:

- 68<sub>10</sub>

- 178<sub>10</sub>

- 68<sub>16</sub>

- C7<sub>16</sub>