BUDAPEST UNIVERSITY OF TECHNOLOGY AND ECONOMICS FACULTY OF ELECTRICAL ENGINEERING AND INFORMATICS DEPARTMENT OF MEASUREMENT AND INFORMATION SYSTEMS

# The MiniRISC processor

Béla Fehér, Tamás Raikovich, Attila Fejér BUTE DMIS

BME-MIT

FPGA labor

#### Contents

#### 1. Introduction

- 2. Internal structure of the MiniRISC CPU

- Datapath

- Control unit

- 3. Application of the MiniRISC CPU

- Signal interfaces

- I/O extension (with examples)

- MiniRISC system

- 4. Development environment

- MiniRISC assembler

- MiniRISC IDE

- Software development (with examples)

# MiniRISC processor - Introduction

- 8-bit microprocessor for simple applications

- Fits in well with the complexity of the LOGSYS Spartan-3E FPGA board

- Low resource requirement

- Harvard architecture

- 256 x 16 bit program memory

- 256 x 8 bit data memory

- Simple RISC instruction set

- Load/store architecture

- 16 x 8 bit internal register file

- Operations on register file only

# MiniRISC processor - Introduction

- Simple RISC instruction set

- Data moving instructions

- Arithmetic instructions (+, -, compare)

- Logic instructions (AND, OR, XOR, bit test)

- Shift, rotate and swap instructions

- Program control instructions

- Operands: two registers or a register and an 8-bit constant

- Absolute and register indirect addressing modes

- Zero (Z), carry (C), negative (N), overflow (V) status bits

- Conditional jump instructions for testing

- Jumps can be done to the whole program memory address range

#### Contents

- 1. Introduction

- 2. Internal structure of the MiniRISC CPU

- Datapath

- Control unit

- 3. Application of the MiniRISC CPU

- Signal interfaces

- I/O extension (with examples)

- MiniRISC system

- 4. Development environment

- MiniRISC assembler

- MiniRISC IDE

- Software development (with examples)

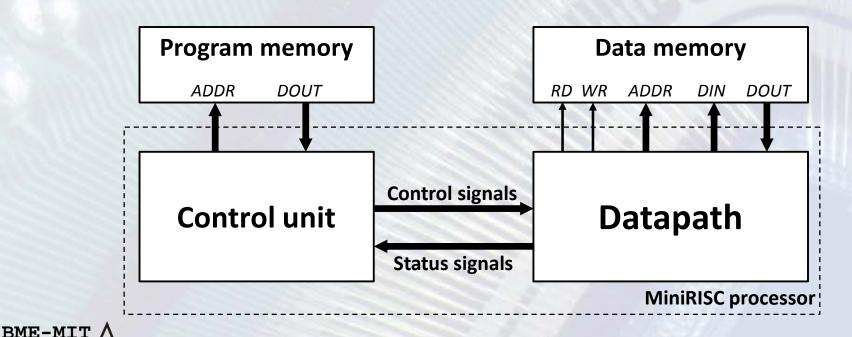

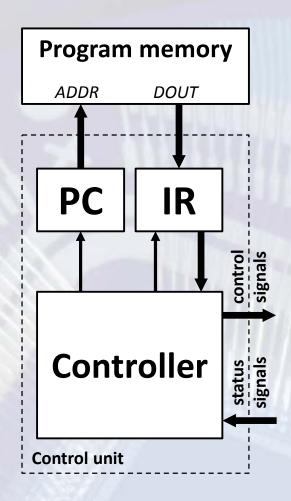

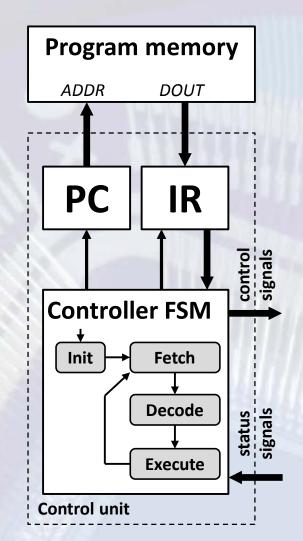

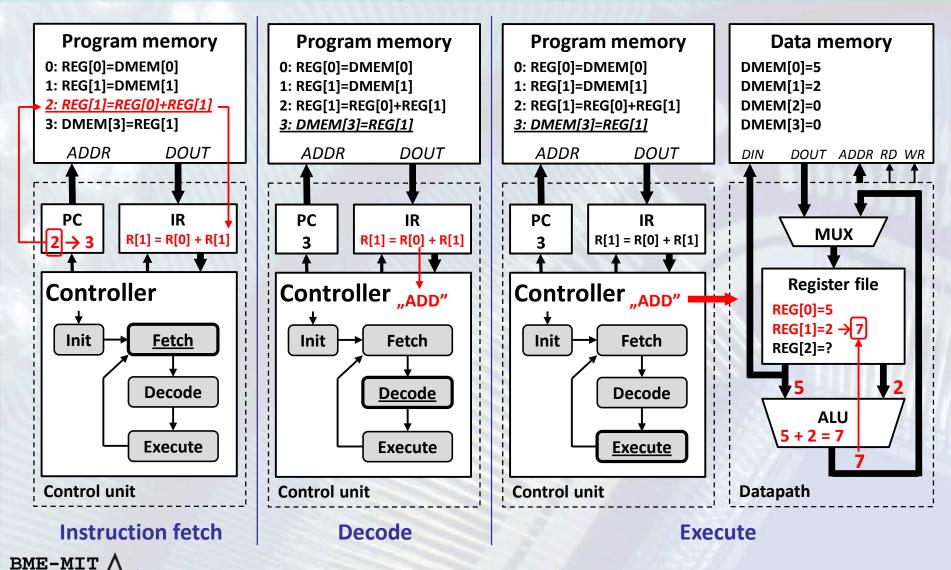

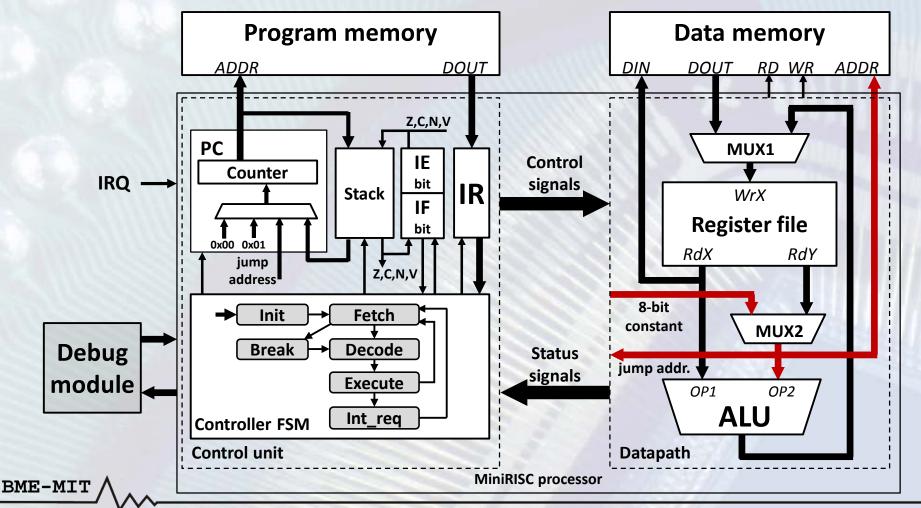

#### Its internal structure follows the RTL design method:

- Control unit: fetching and processing the instructions, and controlling the datapath accordingly

- Datapath: executing the operations on the data

FPGA labor

(Datapath)

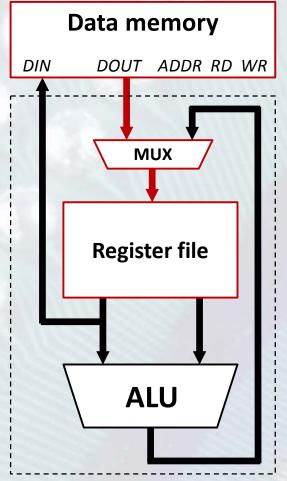

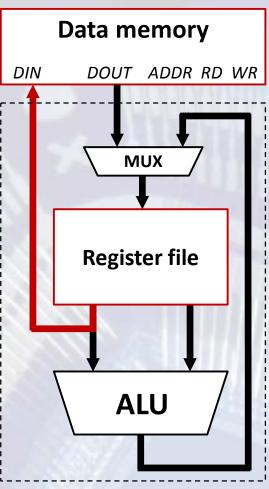

- The operations are executed on the data in the datapath

- Main steps of the data processing:

- 1. Loading the data

- 2. Transforming these data

- 3. Storing the result

- The basic datapath therefore:

- Reads and writes the external data memory where the main data exists

- Contains a register file to hold the data locally

- Contains an arithmetic-logic unit (ALU) to transform the local data

(Datapath)

**Data memory read (load)**

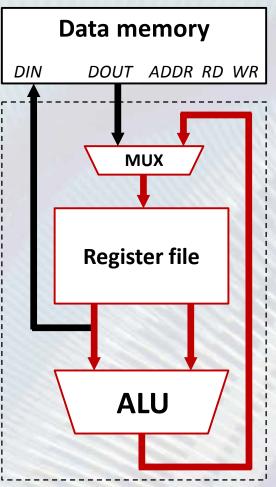

Transforming the local data (ALU operation)

Data memory write (store)

(Datapath of the MiniRISC processor)

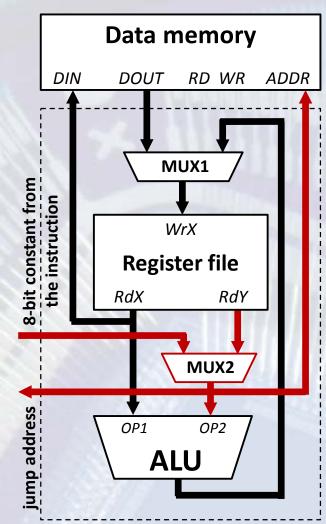

- Extended version of the basic datapath

- Write data select multiplexer for the register file (MUX1)

- ALU result or data memory

- 16 x 8 bit register file

- Two register addresses are used

- Arithmetic-logic unit (ALU)

- Selecting the 2nd ALU operand (MUX2)

- Register

- 8-bit constant from the instruction

- Selecting the addressing mode (MUX2)

- Absolute: address is from the instruction

- Indirect: address is from the register file

(Datapath of the MiniRISC processor – Register file)

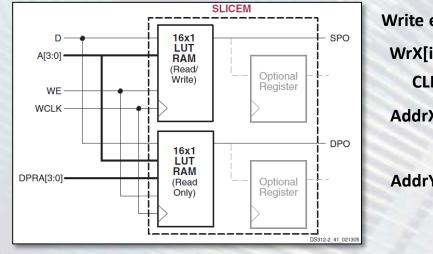

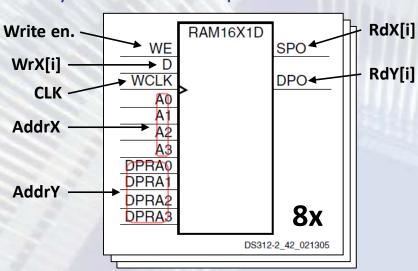

- The register file is implemented using distributed RAM (FPGA resource)

- Distributed RAM can be used to store small amount of data efficiently

- 1 write port and 1 or 2 read ports

- The write and the first read port has shared address input (A=AddrX)

- The address for the second read port can be different (DPRA=AddrY)

- The write operation is synchronous

- Happens after the clock event (rising or falling edge) if enabled (WE=1)

- The read operation is asynchronous

- The addressed data appears "immediately" on the data output

BME-MIT

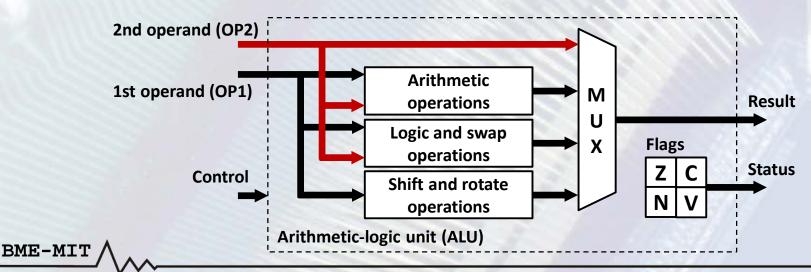

(Datapath of the MiniRISC processor - ALU)

- The ALU executes different operations on the local data

- Data moving: no operation, the result is OP2

- Arithmetic: addition and subtraction with or without carry

- Logic: bitwise AND, OR, XOR

- Shift, rotate and swap

- Status flags give information about the result of the operations

- Zero (Z), carry (C), negative (N) and overflow (V) status flags

- Their value can be tested using the conditional jump instructions

(Datapath of the MiniRISC processor - ALU)

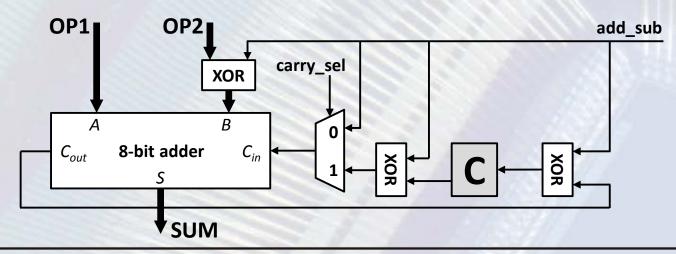

#### Arithmetic operations

In case of the Xilinx FPGAs, the adder/subtractor circuit doesn't have carry input (C<sub>in</sub>), therefore the arithmetic operations are implemented by the following way:

• Addition without carry:  $\{C_{out}, SUM\} = OP1 + OP2 + 0$

• Addition with carry:  $\{C_{out}, SUM\} = OP1 + OP2 + C_{in}$

• Subtraction without borrow:  $\{\overline{C_{out}}, SUM\} = OP1 + \overline{OP2} + 1$

• Subtraction with borrow:  $\{\overline{C_{out}}, SUM\} = OP1 + \overline{OP2} + \overline{C_{in}}$

BME-MIT

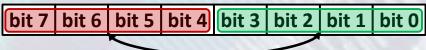

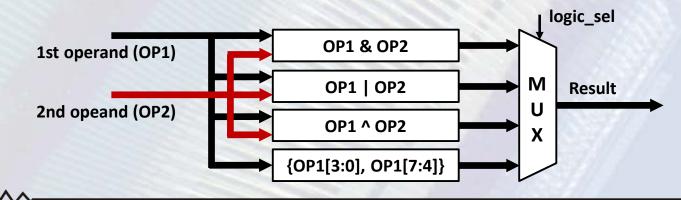

(Datapath of the MiniRISC processor – ALU)

- Logic operations

- Bitwise AND, OR and XOR operations

- Swap operation

- Swapping the lower and upper 4 bits of the 1st operand

1st operand (OP1)

- Implemented in the logic operation block

- The 4th input of the MUX can be used for the swap operation

- Same status flags are modified (Z and N) → same control

BME-MIT

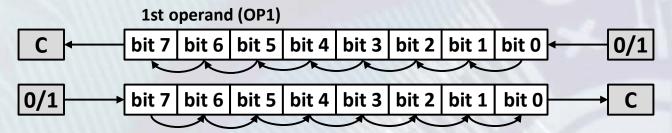

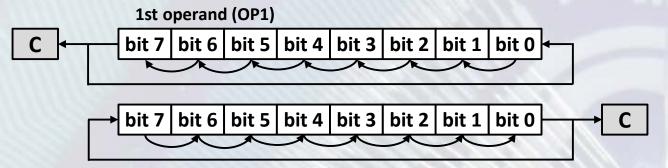

(Datapath of the MiniRISC processor - ALU)

#### Logic shift

- The shift direction can be left or right

- The shifted in bit can be 0 or 1, the shifted out bit is stored in the C flag

#### Arithmetic shift right

- When a signed number is shifted right, the value of the sign bit (MSb) should be preserved in order to get correct result

- The shifted out bit is stored in the carry (C) flag

- There is no separate arithmetic shift left operation because it is the same as the logical shift left operation

(Datapath of the MiniRISC processor - ALU)

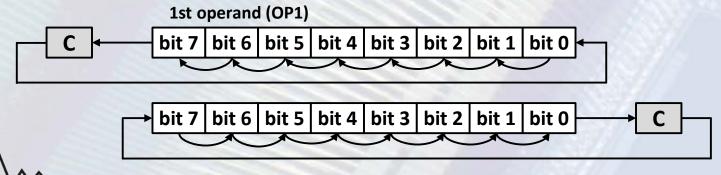

#### Normal rotate

- The rotate direction can be left or right

- The shifted out bit is shifted in at the other side

- The shifted out bit is stored in the carry (C) flag

Rotate through the carry (C) flag

BME-MIT

(Datapath of the MiniRISC processor – ALU)

- The ALU status bits give information about the result of the operations

- Zero bit (Z)

- Indicates if the result of the operation is zero

- The data moving operations don't change the Z flag

- Carry bit (C)

- Indicates if carry has been generated by the arithmetic operations

- In case of shift/rotate operations, the shifted out bit is stored here

- Negative bit (N)

- Two's complement sign bit, the MSb (bit 7) of the result

- The data moving operations don't change the N flag

- Overflow bit (V)

- Indicates the two's complement overflow

- The result of the arithmetic operation cannot be represented using 8 bits

- Detection: the sign bit of the operands are the same but the sign bit of the result is different (the  $C_{in7}$  xor  $C_{out7}$  method cannot be used because the carry in bit of the MSb is not available inside the FPGA)

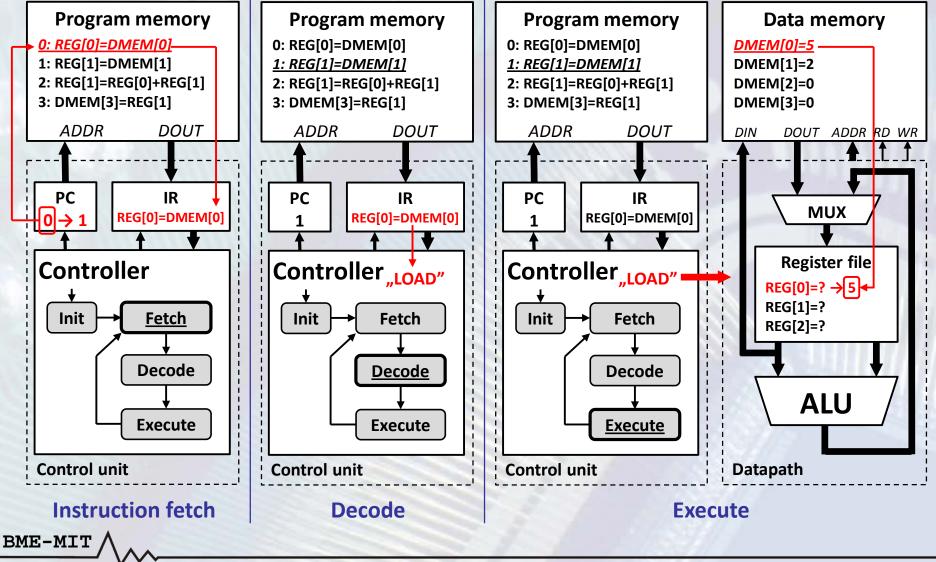

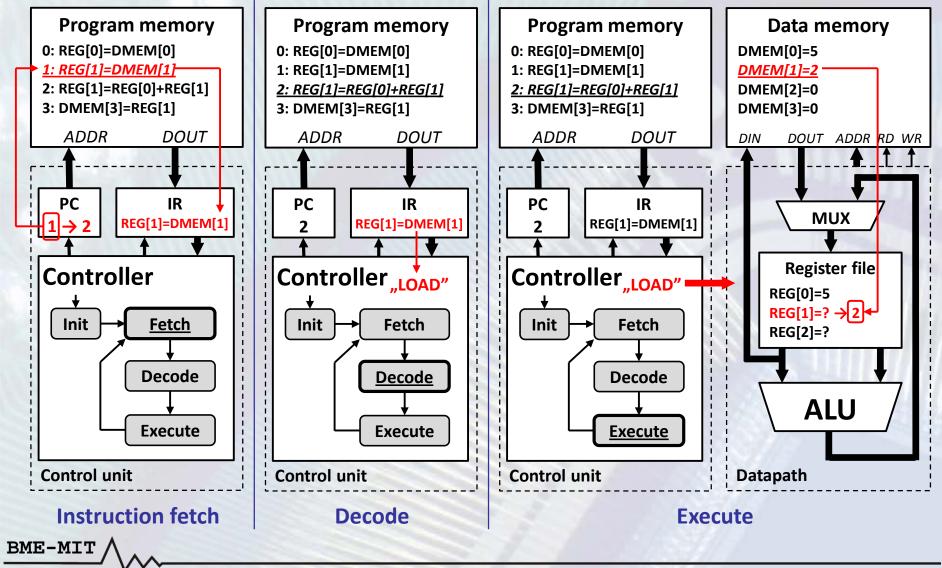

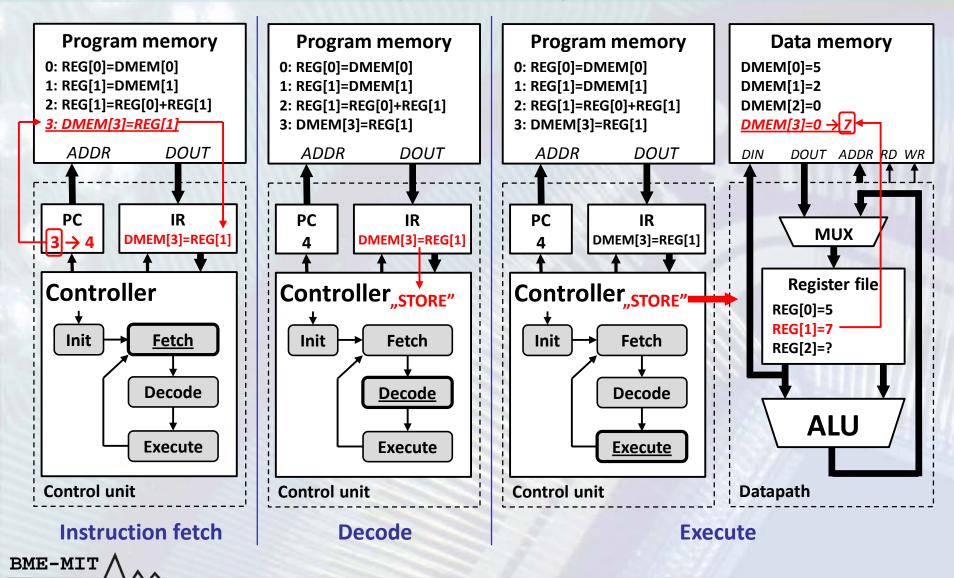

- Example: DMEM[3] = DMEM[0] + DMEM[1], this requires 4 datapath operations:

- 1. REG[0] = DMEM[0] (load)

- 2. REG[1] = DMEM[1] (load)

- 3. REG[1] = REG[0] + REG[1] (ALU operation)

- 4. DMEM[3] = REG[1] (store)

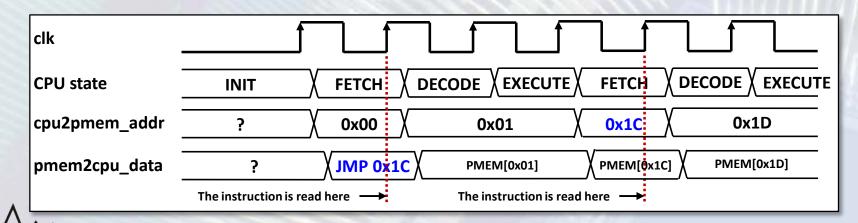

- Instruction: operation that the CPU can execute

- Program: series of instructions

- The given task has to be decomposed into processor-supported instructions

- The program is stored in the program memory

- The control unit reads the instructions and executes them on the datapath

- Program Counter (PC): generates the address of the current instruction

- Instruction Register (IR):

stores the instruction read from the prg. mem.

- To carry out each instruction, the control unit does the following steps:

- Fetch: reading the instruction from the program memory and incrementing the program counter

- Decode: determining the operation and its operands

- Execute: carrying out the instruction's operation using the datapath

- The controller can be an FSM

- One state of the controller FSM can be associated to each step above

- In this case, processing an instruction requires three clock cycles

(Control unit)

- The program memory contains the instructions in form of binary code (machine code)

- The processor cannot interpret higher-level descriptions

- Every instruction contains the description of the operation (opcode) and the other required data (operands)

operation (4 bits)

reg. address (4 bits)

mem. address (8 bits)

#### **Program memory**

|              |                          | •                      |               |

|--------------|--------------------------|------------------------|---------------|

| <u>Addr.</u> | <u>Operation</u>         | Machine code (16 bits) | Assembly code |

| 0:           | REG[0] = DMEM[0]         | 1101000000000000       | MOV r0, 0x00  |

| 1:           | REG[1] = DMEM[1]         | 1101000100000001       | MOV r1, 0x01  |

| 2:           | REG[1] = REG[0] + REG[1] | 1111000100000000       | ADD r1, r0    |

| 3:           | <b>DMEM[3] = REG[1]</b>  | 1001000100000011       | MOV 0x03, r1  |

(Control unit of the MiniRISC CPU – Instruction set)

- Instruction set: list of the allowed instructions and their representation in memory

- Basically, an instruction is a binary number

- Machine code

- Structure of the instructions

- Opcode: determines the operation to be executed

- Operands: data used by the given operation

- Register

- Constant value

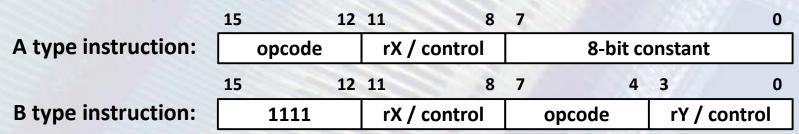

(Control unit of the MiniRISC CPU - Instruction set)

- The size of the MiniRISC instructions is 16 bits in order to use the FPGA resources more efficiently (less prg. mem. size)

- The register file contains 16 registers

- Register operand: 4-bit address

- 16 register is enough for most of the tasks

- 16-bit instructions → more registers are not possible

- 8-bit datapath

- Constant operand: 8-bit value

- Operations with constants are very common, therefore the usage of constant operands in case of ALU operations greatly reduces the program size

- 256 word program and data memory → 8-bit mem. address

24

The whole address range can be covered using absolute or register indirect addressing

(Control unit of the MiniRISC CPU – Instruction set)

- How many operands should be in the 16-bit instructions?

- Separate addresses for each port of the register file

- The program contains less number of instructions

- The instructions are wider

- Operands: 12 bits

- Two source register (rX, rY) and a destination register (rD)

- One register (rD) and an 8-bit constant

- Opcode: 4 bits → 16 possibile opcodes

- 16 opcodes are not enough for the MiniRISC processor!

(Control unit of the MiniRISC CPU – Instruction set)

- How many operands should be in the 16-bit instructions?

- Two register addresses

- Good tradeoff between the number of instructions and the length of instructions

- Two main instruction type according to the operands

- A register (rX) and an 8-bit constant → 12 bits

- Two registers (rX and rY, rX is the dest. reg.) → 8 bits

B type

- Opcode: 4 bits + 4 bits

- A type: 15 opcodes (B type is indicated by the 1111 prefix)

- B type: 16 opcodes

- 31 opcodes together, this is enough for the MiniRISC processor

(Control unit of the MiniRISC CPU - Instruction set)

- An instruction is a binary number (machine code)

- Machine code is hard to work with → assembly code

- The assembly code uses mnemonics

- Mnemonic: short word, refer to the operation

- For example: ADD addition, MOV data movement, etc.

- Operands of the MiniRISC instructions can be:

- Register: r0 r15

- Constant: #0 #255 (for ALU operations)

- Memory address: 0 255 (constant for memory addressing)

- Register for indirect addressing: (r0) (r15)

- The assembler generates the machine code from the assembly code

(Control unit of the MiniRISC CPU – Instruction set)

#### **Data moving instructions**

- Data memory read using absolute or indirect addressing

- Data memory write using absolute or indirect addressing

- Load constant into register

- Move data from register to register

- The value of the ALU status bits is preserved

| Machine code     | Assembly code | Operation       | Z  | С | N  | V   |

|------------------|---------------|-----------------|----|---|----|-----|

| 1101xxxxaaaaaaaa | MOV rx, addr  | rX ← DMEM[addr] | -  | - | -  | -   |

| 1111xxxx1101yyyy | MOV rx, (ry)  | rX ← DMEM[rY]   | -  |   | #= | 1-7 |

| 1001xxxxaaaaaaaa | MOV addr, rX  | DMEM[addr] ← rX | -  | - | -  | -   |

| 1111xxxx1001yyyy | MOV (rY), rX  | DMEM[rY] ← rX   | -/ | - | -  | -   |

| 1100xxxxiiiiiiii | MOV rx, #imm  | rX ← imm        | -  | - | -  | -   |

| 1111xxxx1100yyyy | MOV rx, ry    | rX ← rY         | -  | - | -  | -   |

(Control unit of the MiniRISC CPU - Instruction set)

#### **Arithmetic instructions**

- Addition and subtraction with or without carry

- Compare (subtraction without storing the result)

- Operands: two registers or a register and an 8-bit constant

- Some opcode bits are used as datapath control signals

- This way, the controller state machine becomes simpler

| Machine code                    | Assembly code | Operation         | Z | С | N | V |

|---------------------------------|---------------|-------------------|---|---|---|---|

| 00 <mark>00</mark> xxxxiiiiiiii | ADD rX, #imm  | rX ← rX + imm     | + | + | + | + |

| 00 <mark>01</mark> xxxxiiiiiiii | ADC rX, #imm  | rX ← rX + imm + C | + | + | + | + |

| 00 <mark>10</mark> xxxxiiiiiiii | SUB rX, #imm  | rX ← rX – imm     | + | + | + | + |

| 00 <mark>11</mark> xxxxiiiiiiii | SBC rX, #imm  | rX ← rX − imm − C | + | + | + | + |

| 1010xxxxiiiiiiii                | CMP rX, #imm  | rX – imm          | + | + | + | + |

Carry select (0: without carry, 1: with carry)

Operation select (0: addition, 1: subtraction)

1 if the result of the arithmetic operation is not stored

(Control unit of the MiniRISC CPU - Instruction set)

#### **Arithmetic instructions**

- Addition and subtraction with or without carry

- Compare (subtraction without storing the result)

- Operands: two registers or a register and an 8-bit constant

- Some opcode bits are used as datapath control signals

- This way, the controller state machine becomes simpler

| Machine code                                   | Assembly code | Operation                   | Z | С          | N | V |

|------------------------------------------------|---------------|-----------------------------|---|------------|---|---|

| 1111xxxx00 <mark>00</mark> yyyy                | ADD rX, rY    | rX ← rX + rY                | + | +          | + | + |

| 1111xxxx00 <mark>01</mark> yyyy                | ADC rX, rY    | $rX \leftarrow rX + rY + C$ | + | +          | + | + |

| 1111xxxx00 <mark>10</mark> yyyy                | SUB rX, rY    | rX ← rX – rY                | + | +          | + | + |

| 1111xxxx00 <mark>11</mark> yyyy                | SBC rX, rY    | $rX \leftarrow rX - rY - C$ | + | +          | + | + |

| 1111xxxx <mark>1</mark> 0 <mark>10</mark> yyyy | CMP rX, rY    | rX – rY                     | + | ı <b>+</b> | + | + |

Carry select (0: without carry, 1: with carry)

Operation select (0: addition, 1: subtraction)

1 if the result of the arithmetic operation is not stored

(Control unit of the MiniRISC CPU - Instruction set)

#### **Logic and swap instructions**

- Bitwise AND, OR and XOR

- Bit test (bitwise AND without storing the result)

- The A type 0111 is the swap (the B type 0111 is the shift)

- Operands: two registers or a register and an 8-bit constant

- Some opcode bits are used as datapath control signals

| Machine code                    | Assembly code | Operation                            | Z | С          | N | V   |

|---------------------------------|---------------|--------------------------------------|---|------------|---|-----|

| 01 <mark>00</mark> xxxxiiiiiiii | AND rX, #imm  | rX ← rX & imm                        | + | -          | + | 1   |

| 01 <mark>01</mark> xxxxiiiiiiii | OR rX, #imm   | rX ← rX   imm                        | + | -          | + | -   |

| 01 <mark>10</mark> xxxxiiiiiiii | XOR rX, #imm  | rX ← rX ^ imm                        | + | -          | + | 1-1 |

| 01 <mark>11</mark> xxxx00000000 | SWP rX        | $rX \leftarrow \{rX[3:0], rX[7:4]\}$ | + | -          | + | -   |

| 1000xxxxiiiiiiii                | TST rX, #imm  | rX & imm                             | + | n <b>-</b> | + | -   |

Operation select (00: AND, 01: OR, 10: XOR, 11: swap)

1 if the result of the logic operation is not stored

(Control unit of the MiniRISC CPU - Instruction set)

#### **Logic and swap instructions**

- Bitwise AND, OR and XOR

- Bit test (bitwise AND without storing the result)

- The A type 0111 is the swap (the B type 0111 is the shift)

- Operands: two registers or a register and an 8-bit constant

- Some opcode bits are used as datapath control signals

| Machine code                    | Assembly code | Operation    | Z | С | N | V          |

|---------------------------------|---------------|--------------|---|---|---|------------|

| 1111xxxx01 <mark>00</mark> yyyy | AND rx, ry    | rX ← rX & rY | + | - | + | 1          |

| 1111xxxx01 <mark>01</mark> yyyy | OR rX, rY     | rX ← rX   rY | + | - | + | -          |

| 1111xxxx01 <mark>10</mark> yyyy | XOR rX, rY    | rX ← rX ^ rY | + | - | + | 1-1        |

| 1111xxxx1000yyyy                | TST rX, rY    | rX & rY      | + | - | + | 1 <u>-</u> |

Operation select (00: AND, 01: OR, 10: XOR)

1 if the result of the logic operation is not stored

(Control unit of the MiniRISC CPU – Instruction set)

#### Shift and rotate instructions

- Logic and arithmetic shift, normal rotate

- Rotate through the carry (C) flag

- Operands: one register (rX) → the rY register address can be used as a control signal, therefore only one opcode is required

| Machine code      | Assembly code | Operation                          | Z | С | N | V   |

|-------------------|---------------|------------------------------------|---|---|---|-----|

| 1111xxxx011110000 | SLO rX        | $rX \leftarrow \{rX[6:0], 0\}$     | + | + | + | -   |

| 1111xxxx011110100 | SL1 rX        | rX ← {rX[6:0], 1}                  | + | + | + | 1   |

| 1111xxxx011110001 | SR0 rX        | rX ← {0, rX[7:1]}                  | + | + | + | -   |

| 1111xxxx011110101 | SR1 rX        | rX ← {1, rX[7:1]}                  | + | + | + | -   |

| 1111xxxx011111001 | ASR rX        | $rX \leftarrow \{rX[7], rX[7:1]\}$ | + | + | + | - I |

Direction select (0: left, 1: right)

Operation select (0: shift, 1: rotate)

Value of the shifted in bit in case of shift operations

Shift type (0: logic, 1: arithmetic)

(Control unit of the MiniRISC CPU - Instruction set)

#### Shift and rotate instructions

- Logic and arithmetic shift, normal rotate

- Rotate through the carry (C) flag

- Operands: one register (rX) → the rY register address can be used as a control signal, therefore only one opcode is required

| Machine code                                                                 | Assembly code | Operation                          | Z | С | N | V |  |

|------------------------------------------------------------------------------|---------------|------------------------------------|---|---|---|---|--|

| 1111xxxx011110010                                                            | ROL rX        | $rX \leftarrow \{rX[6:0], rX[7]\}$ | + | + | + | - |  |

| 1111xxxx011110011                                                            | ROR rX        | $rX \leftarrow \{rX[0], rX[7:1]\}$ | + | + | + | - |  |

| 1111xxxx01111 <mark>0110</mark>                                              | RLC rX        | rX ← {rX[6:0], C}                  | + | + | + | - |  |

| 1111xxxx011110111                                                            | RRC rX        | $rX \leftarrow \{C, rX[7:1]\}$     | + | + | + | - |  |

| Direction select (0: left, 1: right)  Operation select (0: shift, 1: rotate) |               |                                    |   |   |   |   |  |

Shifted in bit select in case of rotate operations (0: shifted out bit, 1: C flag)

Shift type (0: logic, 1: arithmetic)

(Control unit of the MiniRISC CPU - Instruction set)

#### **Program control instructions**

- Unconditional jump using absolute or indirect addressing (JMP)

- Conditional jump using absolute or indirect addressing (Jxx)

- Can be used for testing the value of the ALU status flags

- Operands: a register (rY) or an 8-bit constant

- The rX register address is not used → selects the operation

- One opcode is enough for the program control instructions

| Machine code                    | Assembly code | Operation         | Z        | С          | N | V   |

|---------------------------------|---------------|-------------------|----------|------------|---|-----|

| 1011 <mark>0000</mark> aaaaaaaa | JMP addr      | PC ← addr         | -        | -          | - | -1  |

| 111100001011yyyy                | JMP (rY)      | PC ← rY           |          | 1          | - | - 1 |

| 1011 <mark>0001</mark> aaaaaaaa | JZ addr       | PC ← addr, if Z=1 | <u> </u> | -          | - | -   |

| 111100011011yyyy                | JZ (rY)       | PC ← rY, if Z=1   |          | ı <b>-</b> | - | -   |

| 1011 <mark>0010</mark> aaaaaaaa | JNZ addr      | PC ← addr, if Z=0 | 9 -      | -          | - | -   |

| 1111 <mark>0010</mark> 10111    | JNZ (rY)      | PC ← rY, if Z=0   | -        | -          | - | -   |

(Control unit of the MiniRISC CPU - Instruction set)

#### **Program control instructions**

- Unconditional jump using absolute or indirect addressing (JMP)

- Conditional jump using absolute or indirect addressing (Jxx)

- Can be used for testing the value of the ALU status flags

- Operands: a register (rY) or an 8-bit constant

- The rX register address is not used → selects the operation

- One opcode is enough for the program control instructions

| Machine code                    | Assembly code | Operation         | Z          | С          | N | V |

|---------------------------------|---------------|-------------------|------------|------------|---|---|

| 1011 <mark>0011</mark> aaaaaaaa | JC addr       | PC ← addr, if C=1 | <b>///</b> | -          | - | - |

| 1111 <mark>0011</mark> 1011уууу | JC (rY)       | PC ← rY, if C=1   |            | 1          |   | - |

| 1011 <mark>0100</mark> aaaaaaaa | JNC addr      | PC ← addr, if C=0 |            | -          | - | - |

| 1111 <mark>0100</mark> 1011yyyy | JNC (rY)      | PC ← rY, if C=0   | 37/        | ı <b>-</b> | - | - |

| 1011 <mark>0101</mark> aaaaaaaa | JN addr       | PC ← addr, if N=1 | 9 -        | -          | - | - |

| 1111 <mark>0101</mark> 1011уууу | JN (rY)       | PC ← rY, if N=1   | -          | -          | - | - |

(Control unit of the MiniRISC CPU - Instruction set)

#### **Program control instructions**

- Unconditional jump using absolute or indirect addressing (JMP)

- Conditional jump using absolute or indirect addressing (Jxx)

- Can be used for testing the value of the ALU status flags

- Operands: a register (rY) or an 8-bit constant

- The rX register address is not used → selects the operation

- One opcode is enough for the program control instructions

| Machine code                    | Assembly code | Operation         | Z        | С          | N | V |

|---------------------------------|---------------|-------------------|----------|------------|---|---|

| 1011 <mark>0110</mark> aaaaaaaa | JNN addr      | PC ← addr, if N=0 | <b>\</b> | -          | - | - |

| 1111 <mark>0110</mark> 1011yyyy | JNN (rY)      | PC ← rY, if N=0   | -        | 1          | - | - |

| 1011 <mark>0111</mark> aaaaaaaa | JV addr       | PC ← addr, if V=1 | -        | -          | - | - |

| 1111 <mark>0111</mark> 1011yyyy | JV (rY)       | PC ← rY, if V=1   |          | ı <b>-</b> | - | - |

| 1011 <mark>1000</mark> aaaaaaaa | JNV addr      | PC ← addr, if V=0 | -        | -          | - | - |

| 1111 <mark>1000</mark> 1011уууу | JNV (rY)      | PC ← rY, if V=0   | 9 -      | -          | - | - |

(Control unit of the MiniRISC CPU - Instruction set)

#### **Program control instructions**

- Subroutine call using absolute or indirect addressing (JSR)

- Return from subroutine (RTS) and from interrupt (RTI)

- Enabling (STI) and disabling (CLI) interrupts

- Operands: a register (rY) or an 8-bit constant

- The rX register address is not used → selects the operation

- One opcode is enough for the program control instructions

| Machine code                    | Assembly code | Operation                                     | Z        | С | N | V   |

|---------------------------------|---------------|-----------------------------------------------|----------|---|---|-----|

| 1011 <mark>1001</mark> aaaaaaaa | JSR addr      | stack ← PC ← addr                             | <b>\</b> | - | - | - 1 |

| 1111 <mark>1001</mark> 1011уууу | JSR (rY)      | stack ← PC ← rY                               | -        | 1 | - | - 1 |

| 1011101000000000                | RTS           | PC ← stack                                    | 1        | - | - | -   |

| 1011101100000000                | RTI           | $\{PC, Z, C, N, V, IE, IF\} \leftarrow stack$ | +        | + | + | +   |

| 1011110000000000                | CLI           | IE ← O                                        | <b>-</b> | - | - | -   |

| 1011110100000000                | STI           | IE ← 1                                        | 9 -      | - | - | -   |

(Control unit of the MiniRISC CPU - Subroutine call)

#### Subroutine

- Part of the code for executing a given task

- Relatively independent from the other parts of the code

- Can be used multiple times → only one instance is necessary

- Special subroutine call and return instructions

- Subroutine call: JSR instruction

- Saves the address of the next instruction (return address) to the **stack**

- Loads the address of the first instruction of the subroutine to the program counter

- Return from subroutine: RTS instruction

- Loads the return address from the stack to the program counter

```

00: start:

00:

mov r0, \#0xc0

mov LD, r0

01:

02:

mov r1, #0

mov r2, #121

03:

04:

mov TM, r2

05:

mov r2, \#0x73

06:

mov TC, r2

07:

mov r2, TS

08: loop:

jsr tmr_wait

cmp r1, #0

09:

stack←PC (0x09)

PC←tmr wait

PC←stack (0x09)

<del>20:</del>tmr_wait:

20:

mov r0, TS

21:

tst r0, \#0x04

22:

iz tmr wait

23:

rts

```

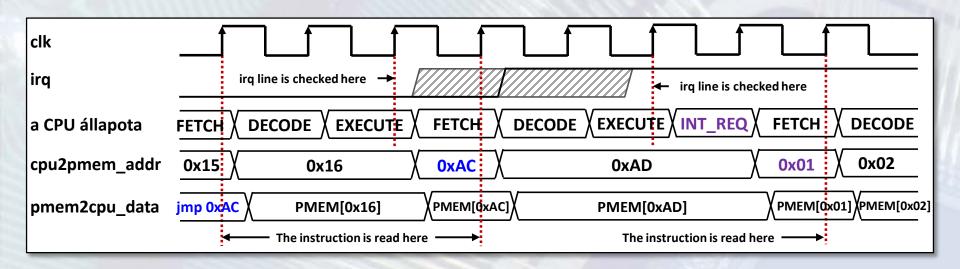

(Control unit of the MiniRISC CPU - Interrupt)

- The instruction execution happens in the order determined by the programmer

- Event handling by polling

$\rightarrow$  slow

- Many times, faster event handling is required → interrupt

- Interrupt

- External request for service

- The CPU can accept it after executing the current instruction

- Interrupt related bits in the control unit of the MiniRISC CPU

- IE (Interrupt Enable) bit: enables the interrupts

- IE=0: the interrupts are disabled (CLI instruction)

- IE=1: the interrupts are enabled (STI instruction)

- IF (Interrupt Flag) bit: indicates the processor state

- IF=0: normal program execution

- IF=1: interrupt service is in progress

- The value of rhe IF bit is available only through the debug interface

(Control unit of the MiniRISC CPU – Interrupt)

- Interrupt system of the MiniRISC CPU

- Active-high interrupt request input (IRQ)

- Simple interrupt system

- Only the signaling comes from the peripheral, identification of the requester is done in software

- The address of the interrupt handler (ISR) is fixed 0x01

- Interrupt servicing in case of the MiniRISC CPU

- Similar to the subroutine call

- If IE=1 and IRQ=1, after executing the current instruction

- The return address and the flags (ALU status bits, IE, IF) are saved to the **stack**

- The interrupt vector (0x01) is loaded into the program counter and the IE bit is cleared

- Returning from interrupt: RTI instruction

- The PC is loaded with the return address and the flags are restored from the stack

```

00:

jmp start

<del>01:___</del>jmp usrt_rx

02: start:

02:

mov r0, #0

03:

mov LD, r0

mov r0, \#0x3b

04:

05:

mov UC, r0

06:

sti

07: loop:

07:

jsr delay

08:

mov r8, #str

09:

jsr print str

0A:

jmp loop

stack \leftarrow \{PC (0x09), flags\}

PC←0x01, IE←0

30: usrt rx:

30:

mov r15, UD

31:

mov LD, r15

32:

rti

```

{PC,flags}←stack

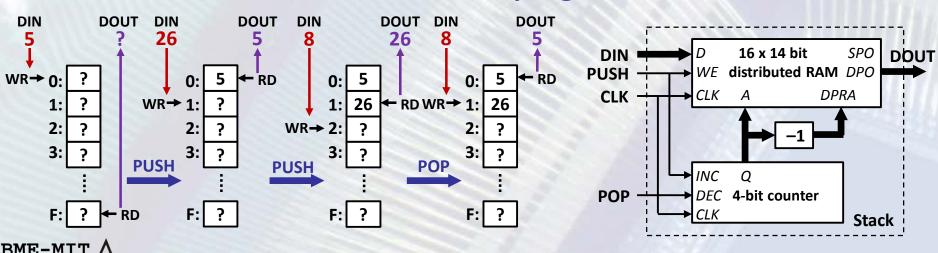

(Control unit of the MiniRISC CPU - Stack)

- The stack is a LIFO (Last-In-First-Out) data storage element

- The last written data can be read first

- Two operations are supported

- Push: writing data to the top of the stack (full stack→overflow)

- Pop: reading data from the top of the stack (empty stack→underflow)

- The type of the stack can be

- Hardware stack inside the processor

- External stack implemented in the data memory

- SP (Stack Pointer) register stores the address of the top of the stack

- The MiniRISC processor contains a 16-word hardware stack

- 16-level subroutine call and interrupt service is possible

- Saved to the stack: program counter (PC), flags (Z, C, N, V, IE and IF)

- RTS instruction: restores the saved PC value

- RTI instruction: restores the saved PC value and the flags

(Control unit of the MiniRISC CPU – Stack)

- A possibile FPGA implementation of the hardware stack

- PC: 8-bit, flags: 6-bit  $\rightarrow$  16 x 14 bit distributed RAM

- The push operation enables the write

- 4-bit bi-directional address counter

- The push op. increments, the pop op. decrements its value

- Read address = write address 1

- The overflow and underflow conditions are not handled in hardware, this is the task of the programmer!

(Control unit of the MiniRISC CPU - IR and PC)

### Instruction Register (IR)

- 16-bit loadable register

- In the fetch phase, the instruction register is loaded with the instruction read from the program memory

### Program Counter (PC)

- 8-bit loadable counter with enable

- Generates the address of the instruction to be fetched

- Load

- Processor initialization: loaded with the reset vector (0x00)

- Interrupt service: loaded with the interrupt vector (0x01)

- Jump and subroutine call: loaded with the jump address

- Return (RTS, RTI): loaded with the return address from the stack

- Enable

- In the fetch phase, its value is incremented in order to address the next instruction

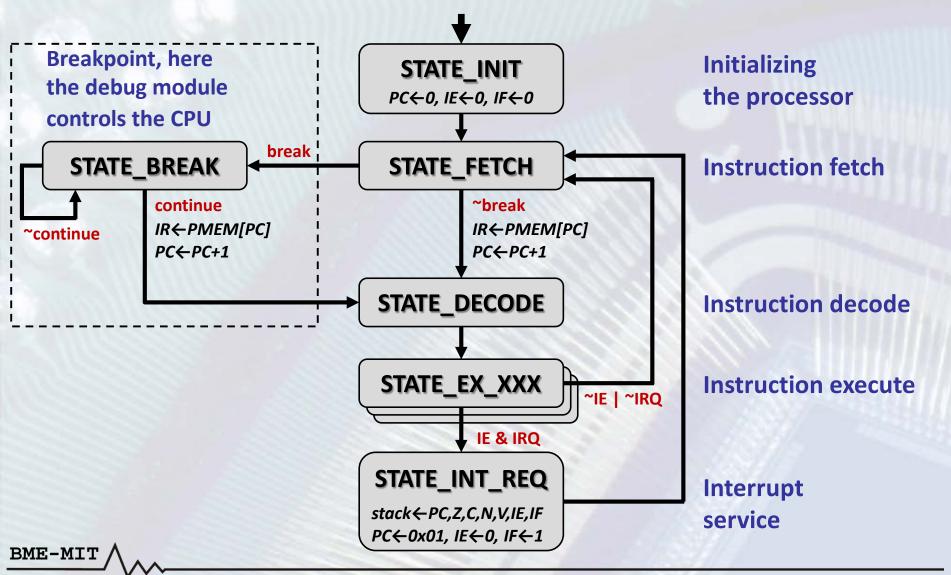

(Control unit of the MiniRISC CPU - Controller FSM)

(Control unit of the MiniRISC CPU - Controller FSM)

- Breakpoint state (STATE\_BREAK)

- Serves software development supporting purposes

- The debug module takes over the control (details later)

- Break signal in the fetch phase → execution stops, BREAK state

- Continue signal in the BREAK state → execution resumes

- Instruction execute

- One state is enough for a group of instructions, because some bits of the instructions are used directly as control signals

- STATE\_EX\_LD: executing data memory read (load)

- STATE\_EX\_ST: executing data memory write (store)

- STATE\_EX\_MOV: load constant, move data from register to register

- STATE\_EX\_ARITH: executing arithmetic operations

- STATE\_EX\_LOGIC: executing logic and swap operations

- STATE\_EX\_SHIFT: executing shift and rotate operations

- STATE\_EX\_CTRL: executing program control instructions

- STATE\_EX\_NOP: no operation (for the unused opcodes)

(Block diagram of the MiniRISC processor)

### The detailed structure can be found in the Verilog source code

### Contents

- 1. Introduction

- 2. Internal structure of the MiniRISC CPU

- Datapath

- Control unit

### 3. Application of the MiniRISC CPU

- Signal interfaces

- I/O extension (with examples)

- MiniRISC system

### 4. Development environment

- MiniRISC assembler

- MiniRISC IDE

- Software development (with examples)

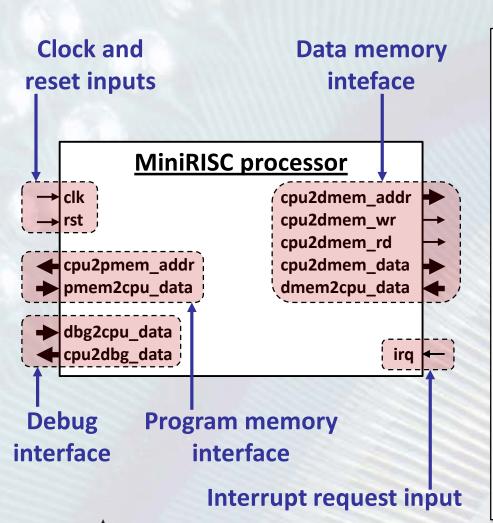

#### Verilog module header:

```

module minirisc cpu(

//Clock and reset.

input wire

clk,

input wire

rst,

//Program memory interface.

output wire [7:0] cpu2pmem_addr,

input wire [15:0] pmem2cpu data,

//Data memory interface.

output wire [7:0]

cpu2dmem_addr,

output wire

cpu2dmem_wr,

output wire

cpu2dmem rd,

output wire [7:0]

cpu2dmem data,

input wire [7:0]

dmem2cpu data,

//Interrupt request input.

input wire

irq,

//Debug interface.

input wire [22:0] dbg2cpu_data,

output wire [44:0] cpu2dbg_data

);

```

(Clock, reset, program memory interface)

- Clock and reset

- clk: system clock (16 MHz), every storage element (flip-flop, memory) operates at the rising clock edge

- rst: active-high reset signal, sets the CPU to the initial state

- Program memory interface

- cpu2pmem\_addr: 8-bit address bus for the program memory

- pmem2cpu\_data: 16-bit data output of the program memory

- The instructions are read in the fetch phase

- In case of jump, the value of the PC can change in the execute phase

- The new valid address appears just in the right time on the address bus

BME-MIT

(Program memory interface)

#### Program memory interface

- In case of jump or subroutine call, the value of the program counter can be changed in the execution phase

- When an interrupt is serviced, the interrupt vector address (0x01) is loaded into the program counter in the INT\_REQ state

- The new programm memory address is available in time for the next instruction fetch phase

(Data memory interface)

- Data memory interface

- Simple synchronous bus, commands are valid at the rising clock edge

- cpu2dmem\_addr: 8-bit address bus

- cpu2dmem\_wr: active-high write enable signal

- cpu2dmem\_rd: active-high read enable signal

- cpu2dmem\_data: 8-bit write data bus (CPU → peripheral)

- dmem2cpu\_data: 8-bit read data bus (peripheral → CPU)

- There are no tri-state drivers inside the FPGA, therefore two separate data bus is required (wrong control of the tri-state drivers would cause short circuit which would damadge the FPGA)

- The MiniRISC processor doesn't have separate I/O interface for the peripherals, therefore the peripherals can be connected to the data memory interface (the peripherals are embedded in the data memory)

- In case of multiple connected peripherals, if the inactive peripherals drive the read data bus with 0, the read data buses can be ORed together and no multiplexer is required

52

Distributed bus multiplexer function

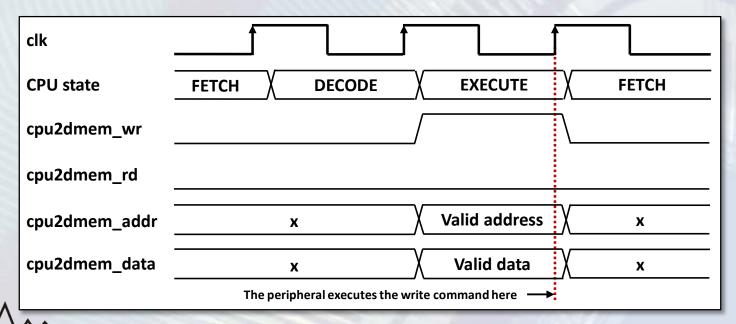

(Data memory interface – Write cycle)

- Write cycle of the data memory interface

- In the execute phase, the write cycle is indicated by the cpu2dmem\_wr signal which is active for 1 clock cycle

- During the write cycle, the cpu2dmem\_addr address is stable

- During the write cycle, the cpu2dmem\_data data is stable, which is sampled by the selected peripheral at the rising edge of the clock

BME-MIT

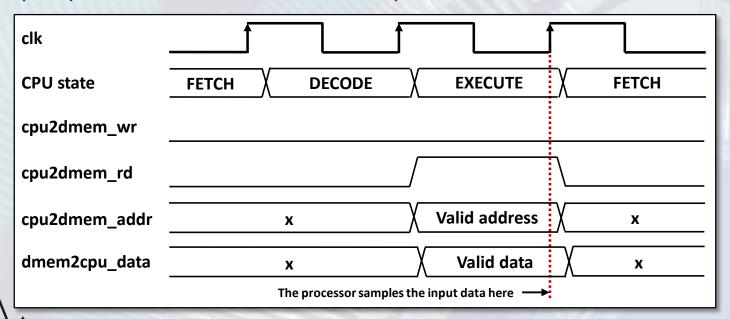

(Data memory interface – Read cycle)

- Read cycle of the data memory interface

- In the execute phase, the read cycle is indicated by the cpu2dmem\_rd signal which is active for 1 clock cycle

- During the read cycle, the cpu2dmem\_addr address is stable

- During the read cycle, the selected peripheral drives the dmem2cpu\_data read data bus with the valid data, the other peripherals drive their data outputs with inactive 0 value

BME-MIT

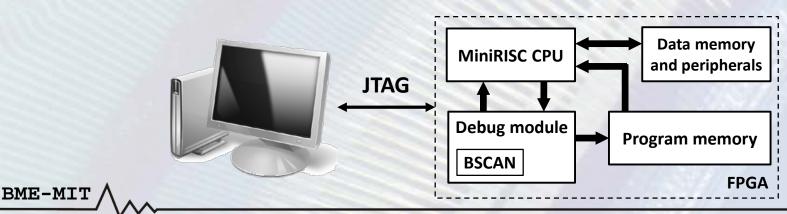

(Debug module, debug interface)

- Debug module: supports the software development

- Gives reset signal to the processor system

- Program download (program memory write)

- Register file, PC and ALU status flags read and write

- Data memory read and write

- Place breakpoint to any program memory address

- Stepping into a breakpoint suspends the execution of the program

- Suspend and resume the execution of the program

- The communication between the debug module and the MiniRISC development environment uses the JTAG interface

(Debug module, debug interface)

#### Verilog module header:

```

module debug module(

//Clock and reser.

input wire

clk,

input wire

rst in,

output wire

rst_out,

//Program memory write interface.

output wire [7:0] dbg2pmem_addr,

output wire [15:0] dbg2pmem_data,

output wire

dbg2pmem_wr,

//Debug interface.

output wire [22:0] dbg2cpu_data,

input wire [44:0] cpu2dbg data

);

```

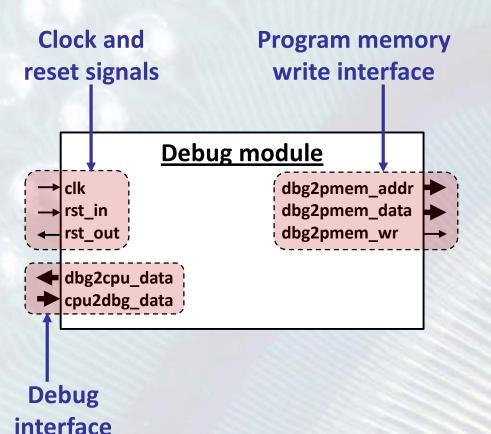

(Debug module, debug interface)

- Interface between the MiniRISC CPU and the debug module

- dbg2cpu\_data: signals from the debug module to the CPU

- cpu2dbg\_data: signals from the CPU to the debug module

- The dbg2cpu\_data input should be driven with 0 if no debug module is in the system

- Other signals of the debug module

- Clock and reset

- clk: system clock (16MHz)

- rst\_in: external reset signal (for example: reset button)

- rst\_out: reset signal for the processor system

- Program memory write interface

- dbg2pmem\_addr: 8-bit address bus

- dbg2pmem\_data: 16-bit write data bus

- dbg2pmem\_wr: active-high write enable signal

# MiniRISC processor – I/O extension

#### Steps of the I/O extension task

- Collecting the requirements according to the type of the peripheral

- Number of registers, their usage mode (writable, readable)

- Command, status, mode select, etc. registers

- Maybe FIFO or small memory block

- Base address assignment, designing the usage of the address range

- Address decoding

- psel = ((cpu2dmem\_addr >> N) == (BASEADDR >> N))

- Size of the address range is 2<sup>N</sup> bytes

- Write enable signals

- xxx\_wr = psel & cpu2dmem\_wr & (cpu2dmem\_addr[N-1:0] == ADDR) +

- Read enable signals

- xxx\_rd = psel & cpu2dmem\_rd & (cpu2dmem\_addr[N-1:0] == ADDR)

- Controls the output MUX: only one multiplexer output is valid at a time, the other peripherals drive their data output with inactive 0

- Also requires when the read causes state change (for example: FIFO)

Checking the lower address bits is required, if N > 0

# MiniRISC processor – I/O extension (Examples)

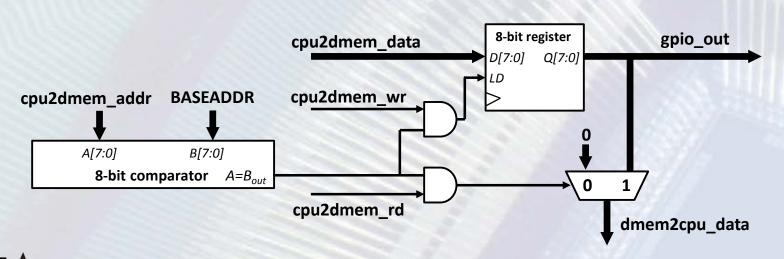

### **Example 1: 8-bit output peripheral with readback**

- Can be used to drive the LEDs on the FPGA board

- Very simple

- A register to store the output data

- BASEADDR + 0x00, 8-bit, writable and readable

- Address decoding logic

- 1 register → 1-byte address range is required

# MiniRISC processor – I/O extension

(Examples)

### **Example 1:** 8-bit output peripheral with readback

```

module basic owr #(

//Base address of the peripheral.

parameter BASEADDR = 8'hff

) (

//Clock and reset.

input wire

clk,

input wire

rst,

//Data memory interface.

input wire [7:0] cpu2dmem_addr,

input wire cpu2dmem wr,

input wire cpu2dmem rd,

input wire [7:0] cpu2dmem data,

output reg [7:0] dmem2cpu_data,

//Output data.

output reg [7:0] gpio_out

);

//Select signal of the peripheral.

wire psel = (cpu2dmem addr == BASEADDR);

```

```

//Data reg. write enable signal.

wire dreg wr = psel & cpu2dmem wr;

//Data reg. read enable signal.

wire dreg rd = psel & cpu2dmem rd;

//Output data register.

always @(posedge clk)

if (rst)

gpio out <= 8'd0;

else

if (dreg wr)

gpio dout <= cpu2dmem data;</pre>

//Driving the read data bus.

always @(*)

if (dreg_rd)

dmem2cpu data <= gpio dout;</pre>

else

dmem2cpu data <= 8'd0;</pre>

endmodule

```

# MiniRISC processor – I/O extension (Examples)

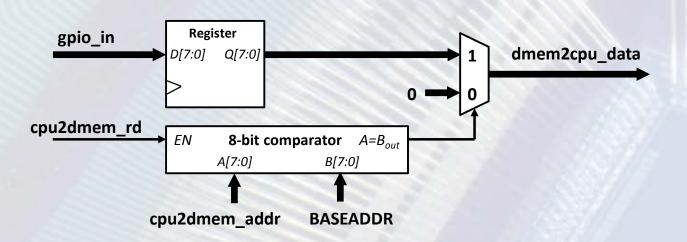

### **Example 2: 8-bit input peripheral**

- Can be used to connect switches or buttons to the system

- Very simple

- A register to sample the input data

- BASEADDR + 0x00, 8-bit, read-only

- Address decoding logic

- 1 register → 1-byte address range is required

# MiniRISC processor – I/O extension

(Examples)

### **Example 2: 8-bit input peripheral**

```

module basic in #(

//Base address of the peripheral.

parameter BASEADDR = 8'hff

) (

//Clock and reset.

input wire

clk,

input wire

rst,

//Data memory interface.

input wire [7:0] cpu2dmem addr,

input wire

cpu2dmem rd,

output reg [7:0] dmem2cpu_data,

//Input data.

input wire [7:0] gpio_in

);

//Select signal of the peripheral.

wire psel = (cpu2dmem addr == BASEADDR);

```

```

//Data reg. read enable signal.

wire in reg rd = psel & cpu2dmem rd;

//Input data register.

reg [7:0] in reg;

always @(posedge clk)

if (rst)

in_reg <= 8'd0;

else

in reg <= gpio in;

//Driving the read data bus.

always @(*)

if (in reg rd)

dmem2cpu data <= in reg;</pre>

else

dmem2cpu data <= 8'd0;</pre>

endmodule

```

# MiniRISC processor – I/O extension (Examples)

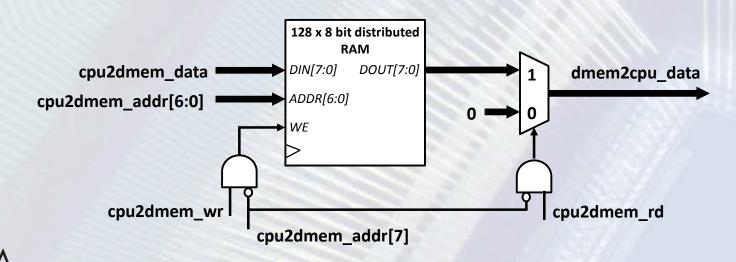

### Example 3: 128 x 8 bit data memory

- Requires 7 address bits

- Address range: 00000000 (0x00) 01111111 (0x7F)

- Address decoding logic

- The lower 7 address bits connected to the memory

- The upper address bit (MSb) is used for address decoding

- If it is 0, the memory is selected

BME-MIT

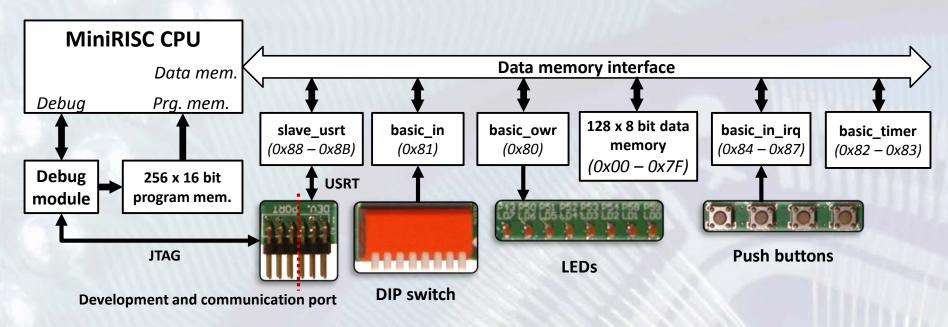

(Simplified MiniRISC system – Block diagram)

| Address range | Size      | Peripheral   | Function                     |

|---------------|-----------|--------------|------------------------------|

| 0x00 - 0x7F   | 128 bytes | data memory  | 128 x 8 bit memory           |

| 0x80          | 1 byte    | basic_owr    | interfacing the LEDs         |

| 0x81          | 1 byte    | basic_in     | interfacing the DIP switch   |

| 0x82 - 0x83   | 2 bytes   | basic_timer  | timing                       |

| 0x84 - 0x87   | 4 bytes   | basic_in_irq | Interfacing the push-buttons |

| 0x88 - 0x8B   | 4 bytes   | slave_usrt   | serial communication         |

(Peripherals – basic\_owr and basic\_in)

- basic\_owr: 8-bit output peripheral with readback

- Simple output, initial value is 0x00

- Data register: BASEADDR + 0x00, writable and readable

- The OUT<sub>i</sub> bit of the data reg. sets the value of the i-th output bit

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| OUT7  | оит6  | OUT5  | OUT4  | OUT3  | OUT2  | OUT1  | оито  |

| R/W   |

- Used for interfacing the LEDs

- basic\_in: 8-bit input peripheral

- Simple input with continuous sampling

- Data register: BASEADDR + 0x00, read-only

- The IN<sub>i</sub> bit of the data reg. gives the state of the i-th input bit

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IN7   | IN6   | IN5   | IN4   | IN3   | IN2   | IN1   | IN0   |

| R     | R     | R     | R     | R     | R     | R     | R     |

Used for interfacing the DIP switch and the push buttons

(Peripherals – basic\_in\_irq)

#### basic\_in\_irq: 8-bit input peripheral with debouncing and interrupts

- Data register

- BASEADDR + 0x00, 8-bit, read-only

- The IN<sub>i</sub> data register bit gives the state of the i-th input bit

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IN7   | IN6   | IN5   | IN4   | IN3   | IN2   | IN1   | IN0   |

| R     | R     | R     | R     | R     | R     | R     | R     |

- Interrupt enable register (IE)

- BASEADDR + 0x01, 8-bit, writable and readable

- The IE; bit enables the interrupt request for the change of the i-th input bit

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IE7   | IE6   | IE5   | IE4   | IE3   | IE2   | IE1   | IE0   |

| R/W   |

- Interrupt flag register (IF)

- BASEADDR + 0x02, 8-bit, writable and readable

- The IF<sub>i</sub> bit indicates the change of the i-th input, write 1 to clear the flag

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IF7   | IF6   | IF5   | IF4   | IF3   | IF2   | IF1   | IF0   |

| R/W1C |

Used for interfacing the 4 push-buttons (the upper 4 register bits are not used)

(Peripherals – basic\_timer)

### basic\_timer: timer peripheral

- Structure: a clock prescaler and an 8-bit down-counter

- The clock prescaler enables the timer counter at given intervals

- Counter initial state register (TR)

- BASEADDR + 0x00, 8-bit, write-only

- The initial state of the counter determines the timer period

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| TR7   | TR6   | TR5   | TR4   | TR3   | TR2   | TR1   | TR0   |

| W     | W     | W     | W     | W     | W     | W     | W     |

- Counter register (TM)

- BASEADDR + 0x00, 8-bit, read-only

- Current value of the timer counter

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| TM7   | TM6   | TM5   | TM4   | TM3   | TM2   | TM1   | TM0   |

| R     | R     | R     | R     | R     | R     | R     | R     |

(Peripherals – basic\_timer)

### basic\_timer: timer peripheral

Command register (TC): BASEADDR + 0x01, 8-bit, write-only

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| TIE   | TPS2  | TPS1  | TPS0  | -     | -     | TREP  | TEN   |

| W     | W     | W     | W     | n.a.  | n.a.  | W     | W     |

• Status register (TS): BASEADDR + 0x01, 8-bit, read-only

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| TIT   | TPS2  | TPS1  | TPS0  | 0     | TOUT  | TREP  | TEN   |

| R     | R     | R     | R     | R     | R     | R     | R     |

| Bit       | Function                                                                                                                              |  |  |  |  |  |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| TEN       | Timer enable bit (0: timer is disabled, 1: timer is enabled)                                                                          |  |  |  |  |  |  |

| TREP      | Timer mode select bit (0: single cycle, 1: repeat)                                                                                    |  |  |  |  |  |  |

| TOUT      | Indicates whether the timer period has been elapsed                                                                                   |  |  |  |  |  |  |

| TPS[2:0]  | Clock prescaler value select bits  0 : no prescale  1 - 7 : 2 <sup>2·(TPS+1)</sup> prescale (16, 64, 256, 1024, 4096, 16384 or 65536) |  |  |  |  |  |  |

| TIE / TIT | Timer interrupt enable / flag (TIT flag is cleared when TS is read)                                                                   |  |  |  |  |  |  |

(Peripherals – basic\_timer)

### basic\_timer: timer peripheral

- Timer period:  $T = (TR + 1) \cdot PS \cdot T_{CLK}$

- TR is the initial value of the timer counter (0 255)

- PS is the prescale (1, 16, 64, 256, 1024, 4096, 16384 or 65536)

- $T_{CLK}$  is the system clock period ( $f_{CLK}$ =16 MHz →  $T_{CLK}$ =62,5 ns)

- The maximum timer period that can be set is 1,048576 s

- After setting the parameters (TR, TPS, TREP), the timer can be started by setting the TEN bit to 1

- In case of single cycle mode (TREP=0), the counter stops after reaching the last state (0). In case of repeat mode (TREP=1) the counter is reloaded with TR after reaching the last state.

- The TOUT bit indicates that the timer period has been elapsed, this bit can be cleared by reading the status register (TS)

- If the interrupt is enabled (TIE=1), the TOUT bit also activates the interrupt request output of the timer

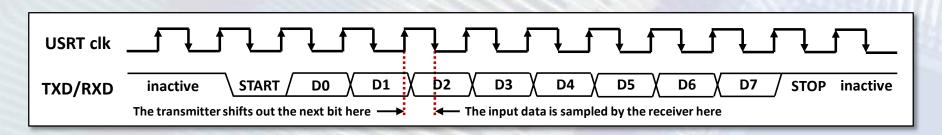

(Peripherals – slave\_usrt)

### slave\_usrt: peripheral that provides serial communication

- USRT (Universal Serial Receiver Transmitter) data transfer

- Data framing: 1 START bit (0), 8 data bits, 1 STOP bit (1)

- USRT clock: determines the communication speed

- The master device outputs the clock to the slave device

- Transfer: the new bit is shifted out at the rising edge of the USRT clock

- Reception: the input is sampled at the falling edge of the USRT clock

- Only the characters without frame error (STOP bit = 1) are stored

(Peripherals - slave\_usrt)

#### slave\_usrt: peripheral that provides serial communication

• Control register (UC): BASEADDR + 0x00, 8-bit, writable/readable

|   | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

|   | 0     | 0     | 0     | 0     | RXCLR | TXCLR | RXEN  | TXEN  |

| 1 | R     | R     | R     | R     | W     | W     | R/W   | R/W   |

| Bit   | Mode | Function                                                      |  |  |  |

|-------|------|---------------------------------------------------------------|--|--|--|

| TXEN  | R/W  | 0: USRT transmitter is disabled 1: USRT transmitter is enable |  |  |  |

| RXEN  | R/W  | 0: USRT receiver is disabled 1: USRT receiver is enabled      |  |  |  |

| TXCLR | W    | Write 1 here to clear the transmit FIFO                       |  |  |  |

| RXCLR | W    | Write 1 here to clear the receive FIFO                        |  |  |  |

- Data register (UD): BASEADDR + 0x03, 8-bit, writable/readable

- Write: write data to the transmit (TX) FIFO (if TXNF=1)

- Read: read data from the receive (RX) FIFO (if RXNE=1)

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| R/W   |

## MiniRISC system

(Peripherals – slave\_usrt)

#### slave\_usrt: peripheral that provides serial communication

FIFO status register (US): BASEADDR + 0x01, 8-bit, read-only

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3  | bit 2 | bit 1 | bit 0   |

|-------|-------|-------|-------|--------|-------|-------|---------|

| 0     | 0     | 0     | 0     | RXFULL | RXNE  | TXNF  | TXEMPTY |

| R     | R     | R     | R     | R      | R     | R     | R       |

- Interrupt enable reg. (UIE): BASEADDR + 0x02, 8-bit, writable/readable

- The FIFO status interrupts can be enabled/disabled here

- The interrupt request is active while the enabled events are active

|   | bit 7 | bit 6 | bit 5 | bit 4 | bit 3  | bit 2 | bit 1 | bit 0   |

|---|-------|-------|-------|-------|--------|-------|-------|---------|

|   | 0     | 0     | 0     | 0     | RXFULL | RXNE  | TXNF  | TXEMPTY |

| ď | R     | R     | R     | R     | R/W    | R/W   | R/W   | R/W     |

| Bit     | Meaning                      |                              |

|---------|------------------------------|------------------------------|

| TXEMPTY | 0: the TX FIFO contains data | 1: the TX FIFO is empty      |

| TXNF    | 0: the TX FIFO is full       | 1: the TX FIFO is not full   |

| RXNE    | 0: the RX FIFO is empty      | 1: the RX FIFO contains data |

| RXFULL  | 0: the RX FIFO is not full   | 1: the RX FIFO is full       |

### Contents

- 1. Introduction

- 2. Internal structure of the MiniRISC CPU

- Datapath

- Control unit

- 3. Application of the MiniRISC CPU

- Signal interfaces

- I/O extension (with examples)

- MiniRISC system

### 4. Development environment

- MiniRISC assembler

- MiniRISC IDE

- Software development (with examples)

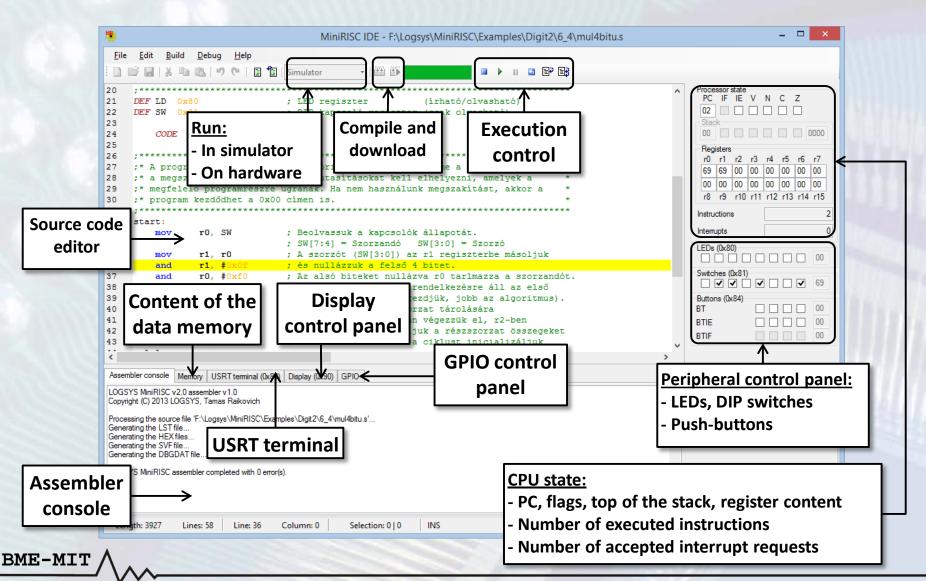

- A development environment (MiniRISC IDE) is available for the MiniRISC system designed for the LOGSYS Spartan-3E FPGA board

- The programs written in assembly language can be compiled using the LOGSYS MiniRISC Lite assembler

- Requires the .NET Framework 4.0 to run (this is the part of the operating system from Windows 8)

- The capabilities of the assembler fit the MiniRISC CPU

- Simple instruction interpretation

- Generates absolute code (no linker)

- No macros

- No address arithmetic

- No conditional compilation

- Stops in case of error

- Running from command line: MiniRISCv2-as filename.s

- Reads the *filename.s* assembly source file, and in case of no error, the following files are generated:

- filename.lst assembly list file with addresses, labels,

identifiers and machine code

• code.hex text file for initializing the program memory

from the Verilog source code

• data.hex text file for initializing the data memory

from the Verilog source code

• **filename.svf** SVF file for initializing the program and data

memories using the LOGSYS GUI

• filename.dbgdat file containing the debug informations

- The error messages appear in the console

- The MiniRISC assembler is integrated with the MiniRISC IDE, therefore it is not common to run the assembler from command line

- Souce file: simple text file with .s extension

- Processed line-by-line: one instruction per source code line

- Format of the assembly source code lines

LABEL: INSTR OP1{, OP2} ; Comment

- LABEL Identifier representing the address of the following instruction

- INSTR

Mnemonic referring to the operation, for example: ADD addition, JMP jump, etc.

- OP1{, OP2} Operands of the instruction, the OP2 is not always present

- ; Comment The ';' character indicates the start of the

- comment which is skipped by the assembler

#### Recommendations

- Write comments for each instruction

- Use the TAB character for formatting the code

- Only few rules exist

- The operands of the instructions can be

- Register

r0 - r15

Constant/immediate #0 – #255

(for ALU operations)

Memory address0 – 255

(constant for memory addressing)

Indirect address (r0) – (r15)

#### Numeric constants

No prefix

decimal

0 - 255

Ox prefix

hexadecimal 0x00 – 0xFF

Ob prefix binary

0b00000000 - 0b11111111

#### Character constants

- A character between the marks (example: # A value: 65)

- Escape sequences: '\", '\", '\\", '\\a', '\\b', '\\f', '\\n', '\\r', '\\r', '\\r'

- **String constants**

- Characters between the " " marks (example: "MiniRISC\r\n")

- Can be used only in the data section

#### Assembler directives

- DEF: assigns an identifier to a constant

DEF SW 0x81 ; Address of the DIP switch

- This is not a CPU instruction. It defines a replacement rule for the assembler, which provides better readability of the source code for the user.

- CODE: indicates the beginning of the code section

- The generated code is placed into the program memory

- DATA: indicates the beginning of the data section

- The generated code is placed into the data memory

- Only labels and DB directives are allowed in the data section

- DB: initializes the data memory with constants

DB "MiniRISC.\r\n", 0 ;0 terminated string

- Can be used only in the data section

- Numeric, character and string constants can follow the DB directive

- The constants are separated with the comma character

- Assembler directives

- ORG: directly defines the start address

ORG memory\_address

- Sets the start address of the following code segment

- Can be used in both code and data sections

- The address and the machine code of the instructions, and the interpretation of the identifiers used by the compiler can be checked in the generated LST file

- If the program has been compiled without errors, it can be built in to the design as a memory initializer data (.HEX output files) or it can be downloaded to the already configured FPGA device (.SVF output file)

#### **Capabilities of the source code editor:**

- Syntax highlighting

- Underlining the wrong source code lines, and displaying the error message if the cursor points to a wrong line

- In case of a compiled program, displaying the value of the identifiers if the cursor points to an identifier

- In case of a downloaded program

- Displaying the value stored in the registers if the cursor points to a register

- In case of indirect addressing, displaying the address and the data if the cursor points to a register

```

sr0 r0 ; A következő állap

jc shr_loo ; A C flag tesztelé

or Unresolved symbol 'shr_loo'. kerül

jmp shr_loop ; Ugrás a ciklus ele

```

- From the simulator dropdown menu, it can be selected whether the program should run

- In the simulator (this option is always available)

- On the hardware (LDCxxx development cable)

- Selection is only possible when the program doesn't run

#### Simulator

- Simulates the processor system implemented in the FPGA with clock cycle precision

- The program execution is slower in this case

- ~400000 instruction/s → ~1,2 MHz system clock frequency

- Most of the peripherals of the MiniRISC system are available in the simulator

- Run on the hardware

- Available only, if the FPGA board is connected to the PC

- Compiling the program: Compile (EE, F5) button

- The error messages appear in the console

- The wrong lines are underlined with red color

- Downloading the compiled program: **Download** ( F6) btn.

- If the FPGA hasn't configured yet, the MiniRISC system is downloaded first

- The execution stops at address 0x00 (reset vector)

- Controlling the execution of the program

- Run (, F7): resumes the execution of the program

- **Break** ( , F8): suspends the execution of the program, the next instruction is highlighted with yellow color

- **Step** (F10): the current instruction is executed and the execution stops at the next instruction

- Controlling the execution of the program

- Auto step ( ): the Step command issued automatically

- The frequency can be set in the Debug menu

- The auto stepping can be stopped using the Break command

- Reset ( , F9): issues a reset signal to the processor system

- Stop ( ): stops the execution of the program

- After the command, the program has to be downloaded again

- Breakpoints can be placed to any assembly instruction in the source code editor by clicking on the margin

- The breakpoint is indicated with a red circle on the margin

```

10 mov r0, SW ; A kapcsolók állapota r0-ba kerül.

11 mov LD, r0 ; A LED-ekre kiírjuk r0 értékét.

12 jmp start ; Ugrás a ciklus elejére.

```

- Stepping to a breakpoint suspends the execution

- Basically, a hardware Break command is issued

- Modifying the processor state and the data memory, and controlling the peripherals is possible only when the execution of the program is suspended (break state)

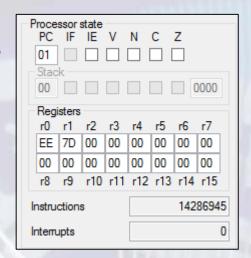

- Processor state panel

- Value of the program counter (PC)

- Value of the flags (Z, C N, V, IE, IF read-only)

- Value of the top of the stack (read-only)

- Value of the registers

- Number of the executed instructions

- Number of the accepted interrupt requests

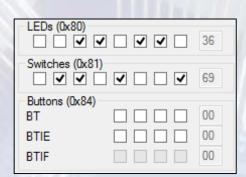

- Control panel of the basic peripherals

- Displays the state of the LEDs, the DIP switches and the push buttons

- Allows register-level control

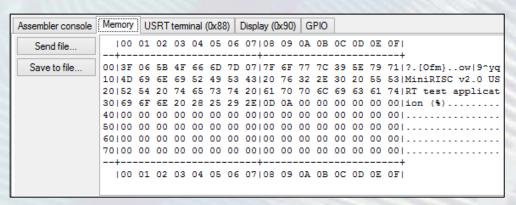

#### Memory window

- Displays the content of the 128 x 8 bit data memory

- Each byte can be modified by clicking on them

- The memory content can be loaded from file (Send file... button) and can be saved to file (Save to file... button)

#### Display window

- Allows controlling the seven-segment and the dot-matrix displays

- The display segments can be turned on/off by clicking on them

- The segment values and the character to be displayed can be specified in the textboxes

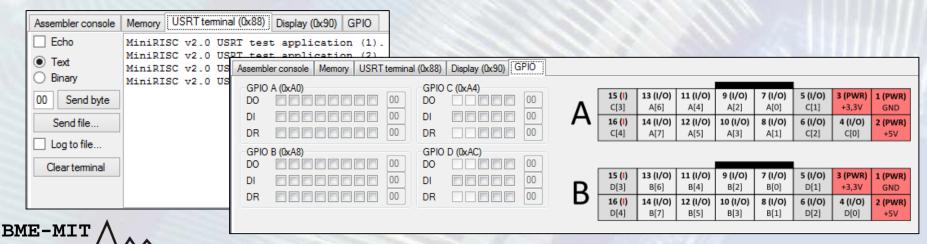

#### USRT terminal window

- Provides serial communication with the MiniRISC system

- The pressed characters will be sent, the received characters are displayed in the terminal window

- Files can be sent, received data can be saved to a file

#### GPIO window

- Displays the state of the GPIO peripherals and provides their register-level control (output data, input data, direction)

- Pinout of the expansion connectors

# Steps of the software development

- Think over the problem and create the basic concept of the solution

- Decompose the problem into MiniRISC assembly instructions and create the source code

- The source code can be compiled using the Compile (F5) command

- If there are errors, correct them

- If the program compiled without errors, it can be downloaded using the *Download (F6)* command

- Verify the operation of the program in debug mode using the services of the MiniRISC IDE

# **Example programs**

### **Example 1:** displaying the state of the DIP switch on the LEDs

Very simple: in an endless loop, read the state of the DIP switch (0x81) and write it to the LEDs (0x81)

```

DEF LD

0x80

; LED register

; DIP switch register

DEF SW

0x81

CODE

;* Start of the program. The addr. 0x00 is the reset vector. *

start:

r0, SW

; Read the state of the sw. to r0.

mov

LD, r0

; Value of r0 is written to the LEDs.

mov

; Jump to the beginning of the loop.

dmt

start

```

# **Example programs**

### **Example 1:** displaying the state of the DIP switch on the LEDs

Content of the list file generated by the assembler

```

LOGSYS MiniRISC v2.0 assembler v1.0 list file

Copyright (C) 2013 LOGSYS, Tamas Raikovich

Source file: example1.s

Created on: 2013.03.27. 12:51:08

S Addr Instr

Source code

; LED register

DEF LD 0x80

DEF SW 0x81

; DIP switch register

CODE

;* Start of the program. The addr. 0x00 is the reset vector. *

C 00

start:

C 00

D081

r0, SW[81]; Read the state of the sw. to r0.

mov

C 01

9080

LD[80], r0

; Value of r0 is written to the LEDs.

mov

B000

; Jump to the beginning of the loop.

C 02

jmp

start[00]

```

90