# Embedded and Ambient Systems 2021.11.30.

#### **FPGA (Field Programable Gate Array)**

- Dynamically configurable devices

- When applying FPGA a system is built up based on basic digital circuit elements

- Motivation:

- Solve problems based on digital HW:

- Rapid operation

- Slow development

- Production time is long

- » In the past (mainly): printed circuit board + discrete logic gates

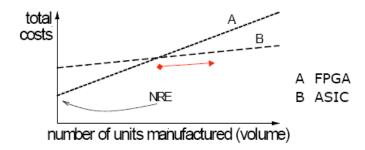

- » Today: ASIC (Application Specific Integrated Circuits)

- » NRE: Non-recurring engineering

- Testing and re-design take a long time: slow iterations

- Time to market is important, therefore the development process needs to be accelerated

- A device is needed that is suitable for the implementation of low level functions but the production and development time is shorter

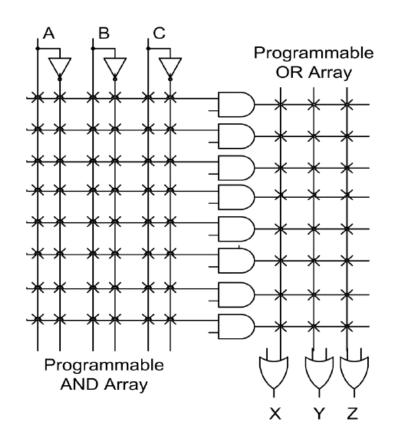

- PLA: Programmable Logic Array

- o In 1970s

- Programmable AND and OR gates

- Implementation of logical functions in canonical form

- Advancement: special circuit for the implementation of complex logic functions

- Drawback: PLSs can be configured during production process and cannot be reconfigured later

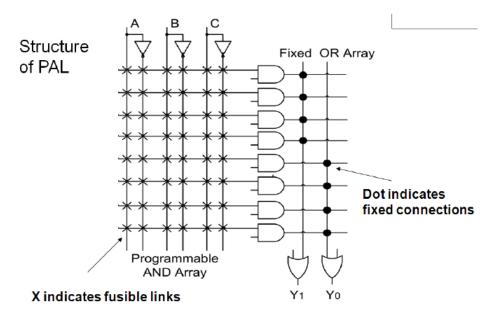

- PAL: Programmable Array Logic

- End of 1970s

- Canonical form

- Programmable input, fixed output

- Less programmed connections: faster signal propagation

- Method of programming

- OTP: one time programmable

- Erasable: using UV light

- Flash kofiguration

- Advancement: PAL can be configured not only during production but also by developper

- Advanced version: GAL (Generic Array Logic)

- Larger complexity, can substitute more PAL device

- Reconfigurable

- Adequate for prototyping

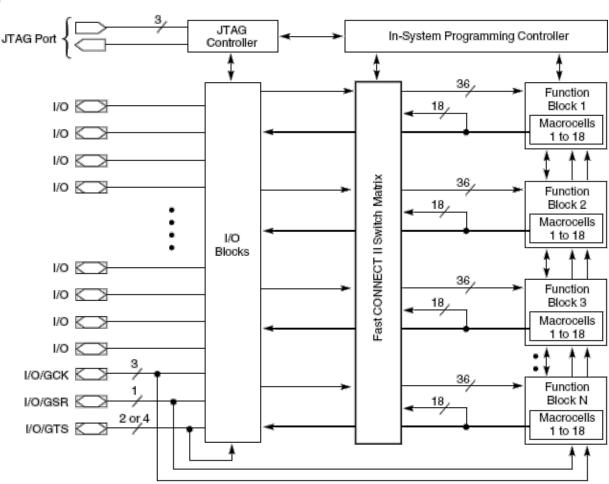

- **CPLD** (Complex Programmable Logic Devices)

- Comlexity: between PAL and GAL

- Architecture:

- **Function block**

- Macrocell

- Wiring matrix

- **Function block: contains** macrocell

- Macrocell: multiple-input single-output logic function (combinational or register output)

- Architecture is similar to PAL

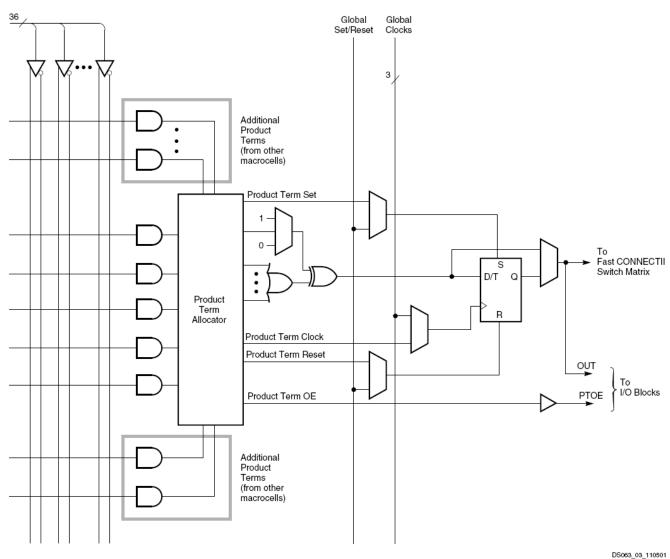

#### **CPLD** macrocell

Architecture of a macrocell: canonical implementation of logic functions

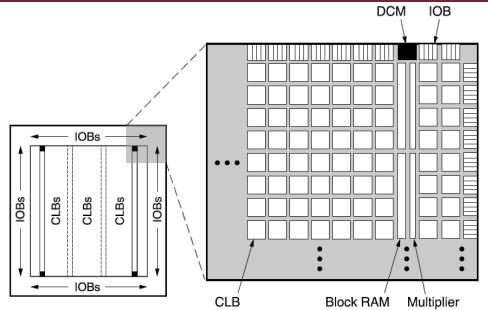

- FPGA: Field Programmable Gate Array

- High-complexity device

- Not necessarily follows the canonical structure

- Several auxiliary components are found

- Clock-management

- Flexible configurable IO block

- Embedded RAM

- Multiplier

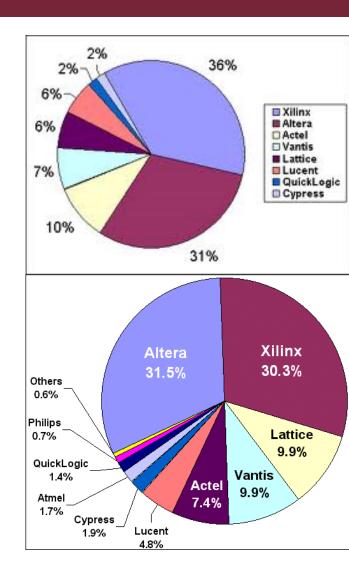

#### FPGA manufacturers

- Some larger manufacturer:

- Xilinx

- Altera

- Actel

- Vantis

- Lattice

- Lucent

- QuickLogic

- Cypress

- o Atmel

- In the followings Xilinx products are used to learn about FPGAs

### Storing the configuration

- Configuration file: contains the internal connections

- **NOT A PROGRAM**

- Word 'programming' mainly refers to downloading the program but in case of FPGA not a program is written instead it is configured how the HW should work (behave)

- The configuration is quite complex and really seems to be a program but it is not a program

- Configuration: making connections between data lines

### Storing the configuration

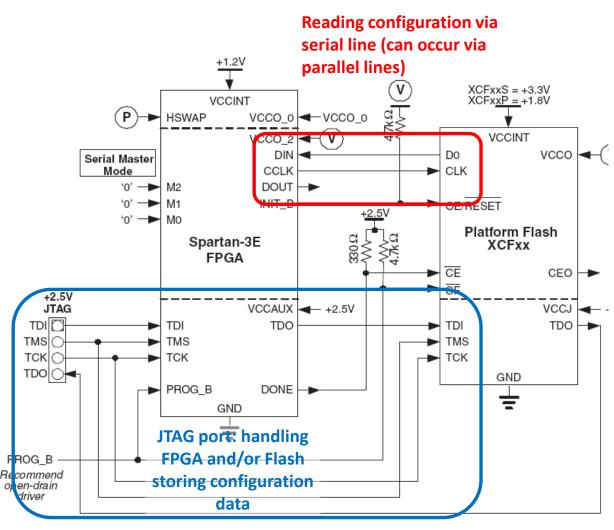

- Reading method of configuration (serial, parallel, JTAG) can be set using external wires

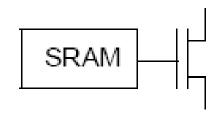

- In FPGAs the configuration data (e.g. connections in a switching matrix) is loaded into an internal SRAM

- Flash-based FPGAs are quite rare now

- SRAM-based configuration allows larger component density ©

- During operation can be reconfigured even partly <sup>©</sup>

- Booting delay of the system is larger: configuration must be loaded into the internal SRAM cells ☺

- Loading configuration: during booting it occurs from external Flash memory or a host PC

- There exist FPGAs containing internal Flash but even in this case booting delay of configuration is inevitable. Their advantage is the smaller area requirement compared to FPGA+Flash and more secure since the configuration process cannot be seen (reverse engineering can be prevented)

**FPGA**

FLASH:

konfig

### Storing the configuration

- FPGAs are reconfigurable during development via a standardized JTAG interface

- JTAG port can be used in a daisy chain toward other devices

- JTAG can be used for writing the external Flash that stores the configuration

- The configuration is stored in the Flash and read from Flash later at FPGA booting

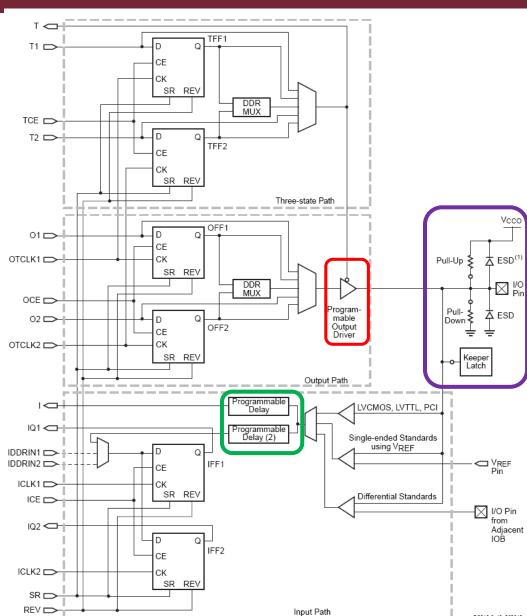

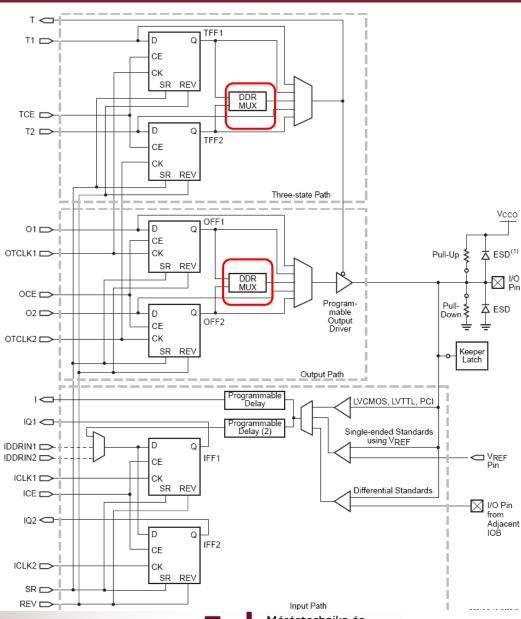

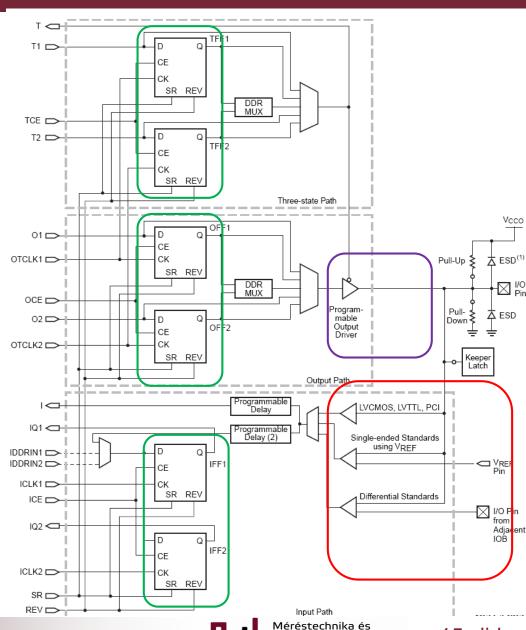

- Flexible configurable Input-Output (IO) block

- Three main signal lines:

- Output drive

- Input lines

- Output lines

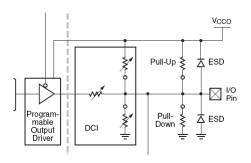

- Programmable input/output setting (see: Programmable Output Driver)

- Programmable pull-up or pull-down resistances

- Keeper latch: can be set that the last value is kept in high-impedance mode and not allow the level floating

- Internal delay lines: input signals are fed directly into the FPGA, the clock signal however get to the IO block via the internal clock division unit and suffers from delay: forcing delay to the data input it can be synchronized with the CLK

- Delay is dynamical, can be configured even during operation

Méréstechnika és

Információs Rendszerek

13.slide

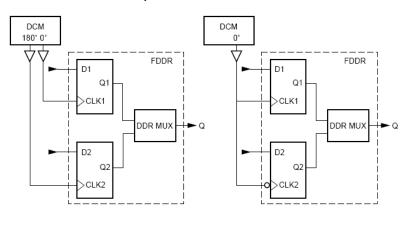

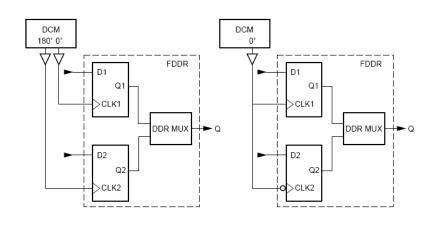

- DDR: Dual-Data-Rate Transmission: data rate is doubled when data transmission occurs for both the rising- and falling edge of the CLK

- D flip-flops used in the conventional manner (triggered for only rising CLK edge) but their CLK signal is designed in a special way:

- 180° phase shift

- inverting

- Writing is done alternately: once into one FF, then into the other FF

- Input and output lines can be synchronized using flipflops to the internal CLK

- Several standardized logic signal level can be applied on the inuts

- TTL levels

- CMOS levels

- o Differential signal inputsdifferenciális jelbemenetek

- Switching threshold voltage via external pin

- Driving can be set:

- o Fast raise up: larger speed with larger noise

- Slow raise up: slower with less noise

- DCI (Digitally Controlled Impedance): to eliminate reflexion: a certain impedance value can be set for the output buffer

Információs Rendszerek

- Configuration of IO pins: in Verilog language find it in user constraints file (ucf)

- o Examples:

- NET "name" IOSTANDARD = "LVTTL";

- O NET "net name" LOC= "P6" | PULLUP;

- In Verilog code they can be given by primitives

- o Example:

```

PULLUP PULLUP_inst (

.O(signal_name) // Pullup output (connect directly to top-level port)

):

```

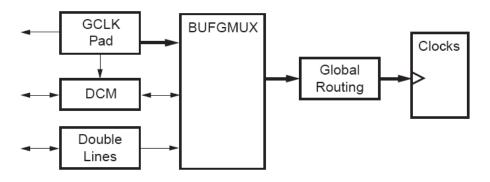

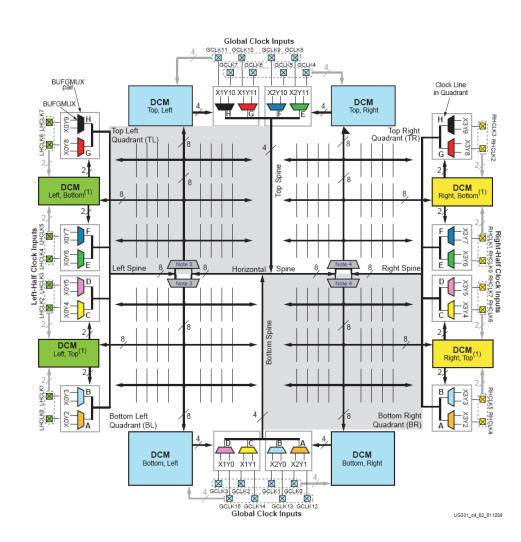

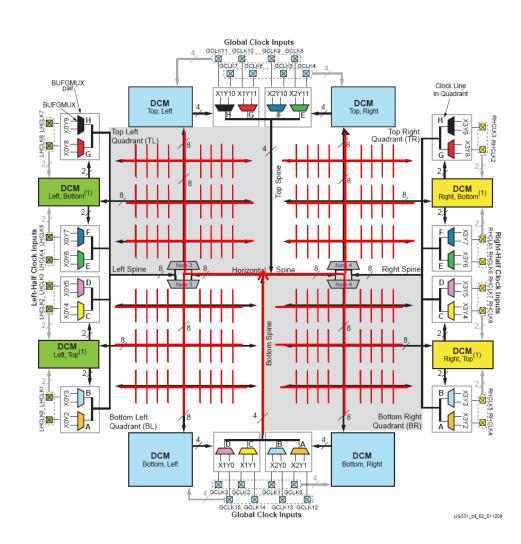

#### **CLK** sources

- CLK signal path:

- CLK input (assigned pins)

- CLK can be received from even more than one input

- Differential CLK input is also possible

- DCM: Digital Clock Management

- BUFMUX: multiplexer to choose CLK source

- Signal on the external CLK pin

- Output of the CLK management unit

- Internal signal

- Clock division unit: Global Routing

- Special wiring network

- The network can be divided into several CLK domain

- Delay is minimal among the different parts of the IC

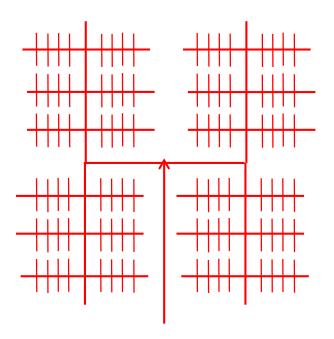

- Fractal-like network structure

- CLK lines are more a less the same in length

- Special wiring network

- The network can be divided into several CLK domain

- Delay is minimal among the different parts of the IC

- Fractal-like network structure

- CLK lines are more a less the same in length

- Special wiring network

- The network can be divided into several CLK domain

- Delay is minimal among the different parts of the IC

- Fractal-like network structure

- CLK lines are more a less the same in length

- Special wiring network

- The network can be divided into several CLK domain

- Delay is minimal among the different parts of the IC

- Fractal-like network structure

- CLK lines are more a less the same in length

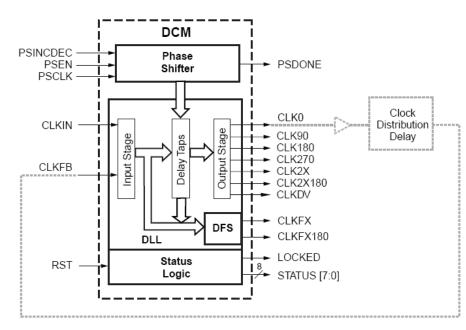

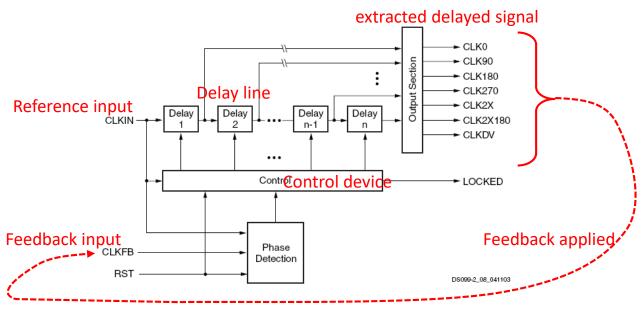

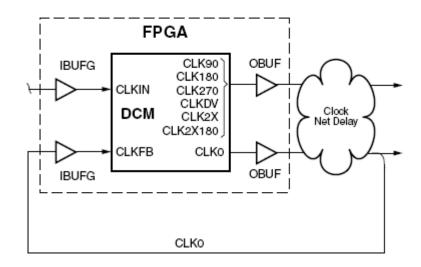

#### DCM: Digital Clock Manager

- DCM used for:

- Eliminating CLK shift

- Phase shifting

- Multiplication/division of CLK frequency

- CLK conditioning, restoring duty cycle of CLK

- CLK buffering, relay

- Capable of generation of high quality CLK from internal signals

- Components:

- Delay Locked Loop (DLL)

- Digital Frequency Synthesizer (DFS)

- Phase Shift (PS)

- Status Logic (SL)

- Internal- and external buffer stages

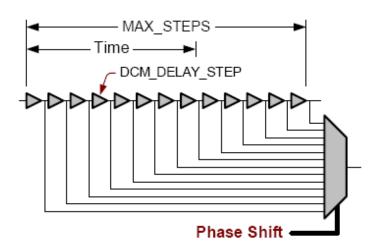

### DCM – phase shift

- Phase shift: the incoming CLK is shifted by a certain value of delay by the appropriate signal extraction from the delay line

- Basically it implements a DLL without feedback

- Example: DDR (Dual Data Rate)

- Generation of negated and not-negated CLK signal

- Is it better than inversion? Yes, since 180° phase-shift can be set accurately: in case of inversion the delay of the inverter should be accounted.

### DCM – delay line & DLL

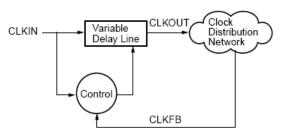

#### Delay Locked Loop

- Similar to phase-locked-loop but now the control is based on the delay between two signals

- The incoming signal is routed to a delay line with variable delay and the delay is tuned until the delay between the two inputs disappears.

### DCM – delay line & DLL

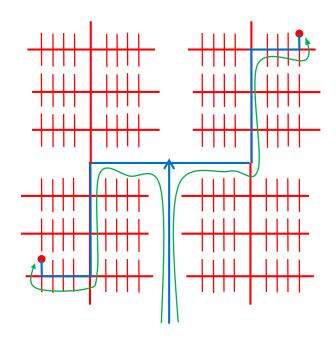

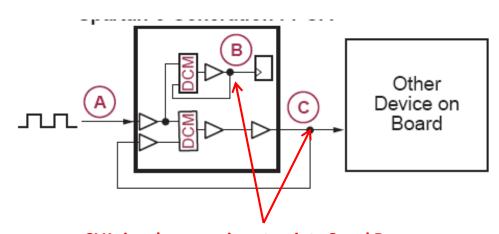

- DLL application: compensation of CLK shift inside or outside of the device:

- CLK signal connected to an internal module or external device is fed back to the DLL input

- DLL sets the delay of the output signal in such a way that no delay occurs between the reference signal and the measured output

- It basically implements a control loop

CLK signals appearing at points C and B are measured and both are controlled by a DCM module based on a common reference (A)

### Considerations in terms of CLK signals

- Design only synchronous logic networks

- Use one CLK signal inside one block

- If slower operation is needed use enabling signals

- Changing between different CLK domains is complicated, avoid it if possible, take care of it during development

- Synthesizer can buffer the CLK inputs in an autonomous manner in normal case

#### Resources

- Main components:

- IO Blocks

- DCM (digital clock management)

- CLB (Configurable Logic Block)

- o RAM

- Multiplier

- Synthesiser usually allocate automatically the resources based on the HW description. Nevertheless it is worth to keep in mind the resources available and their main features since it determines the HW description.

- E.g.: if a shift register does not need a parallel input/output it will not be used up therefore can be implemented more efficiently (see later)

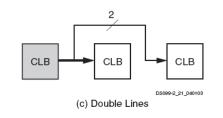

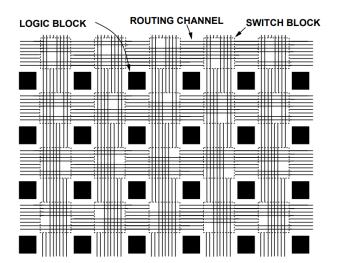

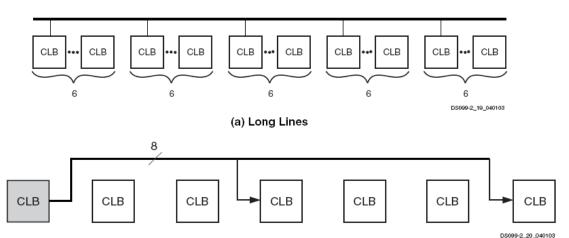

#### Type of connections

- Connections are basically done by the synthesizer

- Different type of connections exist. Basis of grouping: how far the components to be connected are

- Components logically connected should be close to each other physically as well and let them be connected by a 'rapid line'

- There exist direct connections inside a logic, e.g., carry logic (see later)

- For more details: <a href="https://www.xilinx.com/support/documentation/user\_guides/ug331.pdf">https://www.xilinx.com/support/documentation/user\_guides/ug331.pdf</a>

© BME-MIT

(d) Direct Lines

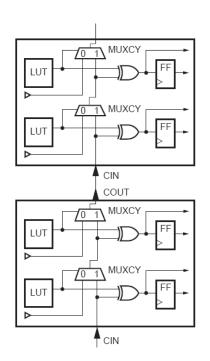

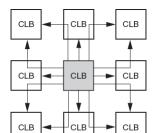

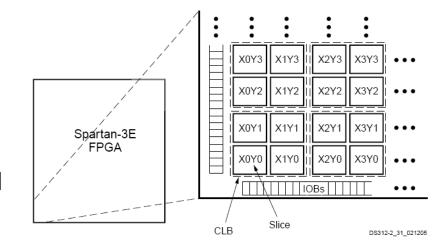

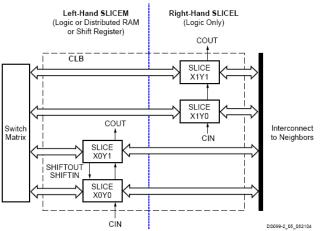

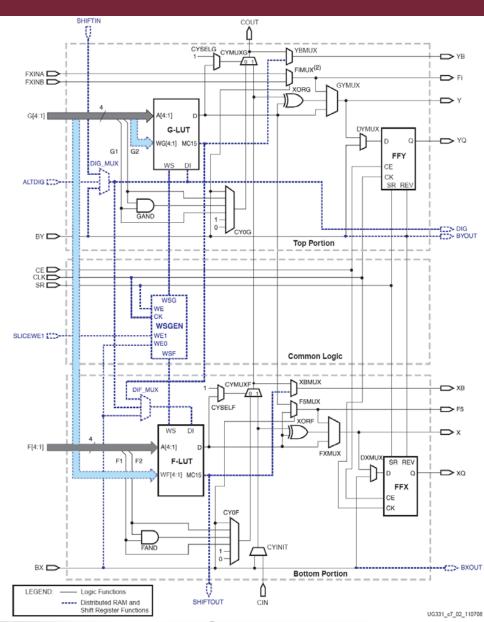

#### **Architecture of CLBs**

- CLB: Configurable Logic Block

- CLB building element: Slice

- 1 CLB conatins 4 slices

- The basic functions of the slices are the same but differences can be found

- CLBs can be connected to each other in several ways

| Device   | CLB<br>Rows | CLB<br>Columns | CLB<br>Total | Slices | LUTs /<br>Flip-Flops | Equivalent<br>Logic Cells | RAM16 /<br>SRL16 | Distributed<br>RAM Bits |

|----------|-------------|----------------|--------------|--------|----------------------|---------------------------|------------------|-------------------------|

| XC3S250E | 34          | 26             | 612          | 2,448  | 4,896                | 5,508                     | 2,448            | 39,168                  |

#### Architecture of a slice

- LUT: look-up table

- Implementation of combinational logic

- Flip-flop:

- Implementation of synchronous logic

- Accelerating arithmetical operation

- carry propagation

- direct AND and XOR gates

- Multiplexers

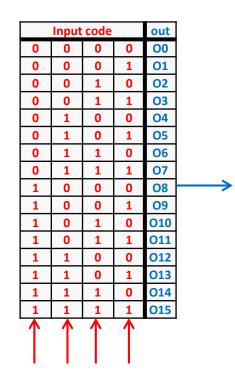

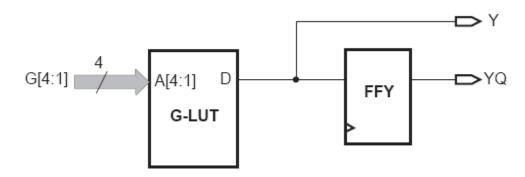

#### LUT: Look-up Table

- LUT: can be sonsidered as a 1-bit wide memory of 4 addressing bits (RAM)

- Implementation of 4-bit input 1-bit output logic functions

- Direct implementation: the output is given to each input code

- If more variables are used then the LUTs inside and outside of the slices can be connected to each other hence expanding the inputs

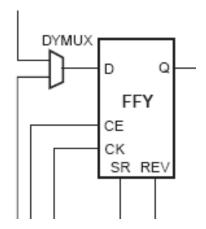

### Flip flop

- Basic component for synchronous digital network

- State machine: combinational logic (LUT)+FF

- Widely configurable

- Set/reset input

- Clock enable

- Data input can be selected

- CLK can be inverted in some cases

- Latch

### Implementation of functional blocks

- Architecture of FPGAs facilitates the implementation of functional blocks

- ALU: arithmetical and logical unit (addition, subtraction)

- multiplication: not always but there exist solutions that support multiplication

- Multiplexer

- Shift regiszter

- o RAM

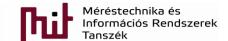

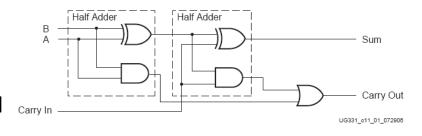

#### **ALU:** addition

- Addition: A xor B xor Carry

- Partial result of inputs A and B is generated by the LUT

- Result (A+B) and the sum with C is generated

by a XOR gate → no need for two LUTs

- carry: determines whether the carry bit shall be propagated or modified:

#### több bites összeadó lánc: