## Embedded and ambient systems 2021.10.13.

# Practice 4 Application of serial port to implement communications via UART

#### Needed during practice

- 01\_EFM32\_User\_guide\_efm32gg-stk3700user\_guide.pdf

- 02\_EFM32\_Schematic\_EFM32GG-BRD2200A-A03schematic.pdf

- 03\_EFM32\_Reference\_manual\_EFM32GGreference\_manual.pdf

- 04\_EFM32\_Datasheet\_efm32gg990\_datasheet.pdf

- Terminal program

Difference between datasheet and user guide:

- -Reference manual contains general info of the whole IC family

- -Datasheet contains specific info of a certain type of IC (from the IC family)

#### UART / USRT / USART

- UART or USRT or USART?

- UART: Universal Asynchronous Receiver/Transmitter

- Serial communication without application of CLK line

- USRT: Universal Synchronous Receiver/Transmitter

- Serial communication based on CLK signal

- USART: Universal Synchronous Asynchronous Receiver/Transmitter

- Since the operation is very similar (main difference is the CLK signal) sometimes both are discussed without distinction

#### **UART** properties

- No CLK signal, i.e., CLK line not needed->less wire

- 2 data lines: transmitter (Tx) and receiver (Rx) line

- Communication speed (=bit duration) has to be set -> defines the bit borders in the system

- Reference oscillators at both the Tx and Rx sides has to be precise otherwise frequency difference will occur between Tx and Rx side and bit duration will change

- If CLK existed it would define the bit borders (as done in USRT)

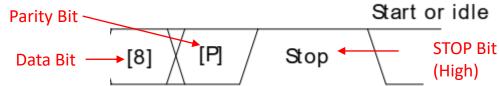

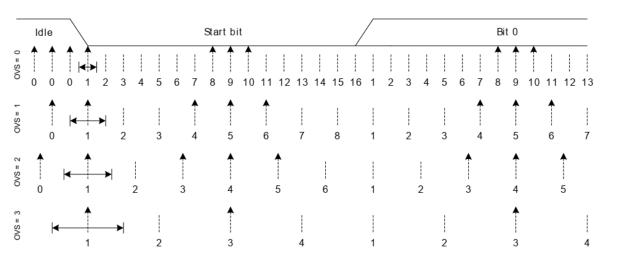

#### **UART** Communications

- Start of communications: edge change from H->L

for 1 bit duration

- Start of frame bit (Start bit)

- Used for synchronization

- Stop or idle

START Bit S O Data Bit

(High-> Low)

Bit border

- Data bits: from 4 up to 16 data bits

- Parity bit (P): optional

- Used for error detection->error is not corrected

- Even parity: count of 1-bits is even->P=0, otherwise

P=1

- Odd parity: count of 1-bits is odd->P=0, otherwise P=1

- End of communications: edge change from L->H

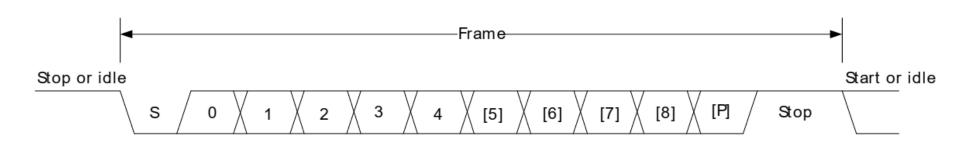

#### **UART Communications**

End of communications: line is High for 1 or 1.5 or

2 bit duration

Full frame:

Refer to page 451 of 03\_EFM32\_Reference\_manual\_EFM32GG-reference\_manual.pdf (Full USART: pp. 449-495)

#### **UART** connection

Checking the datasheet (for IC specific info) is a must -> see page 13.

\_\_\_\_\_

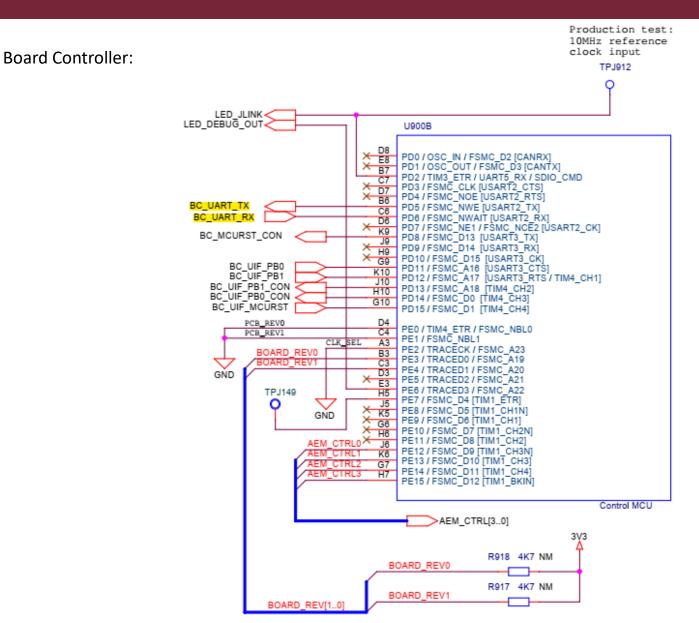

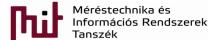

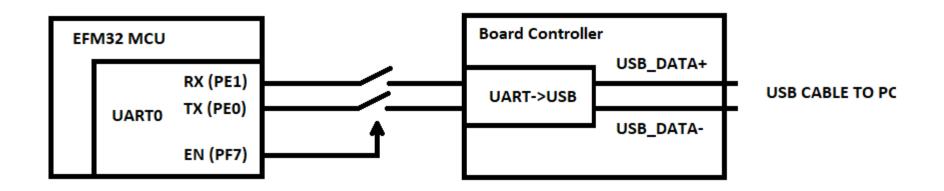

#### 7 Board Controller

The kit contains a board controller that is responsible for performing various board level tasks, such as handling the debugger and the Advanced Energy Monitor. An interface is provided between the EFM32 and the board controller in the form of a UART connection. The connection is enabled by setting the EFM\_BC\_EN (PF7) line high, and using the lines EFM\_BC\_TX (PE0) and EFM\_BC\_RX (PE1) for communicating.

Specific library functions has been provided in the kit Board Support Package that supports various requests to be made to the board controller, such as quering AEM voltage or current. To use these functions, the Board Support Package must be installed. See the Chapter 8 to find out more.

#### Note

The board controller is only available when USB power is connected.

Refer to page 13 of 01\_EFM32\_User\_guide\_efm32gg-stk3700-user\_guide.pdf

#### **UART** connection

Also see page 14.

\_\_\_\_\_

#### 8 Board Support Package

The Board Support Package (BSP) is a set of C source and header files that enables easy access to, and control over some board specific features.

Compared to the Energy Micro development kit, the functionality is limited. Unless you need/want some of the functions contained in the BSP, there is really no need to include or use it. The EFM32 in the Starter Kit is fully usable without BSP support, and you can use all peripherals in the emlib without the BSP.

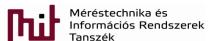

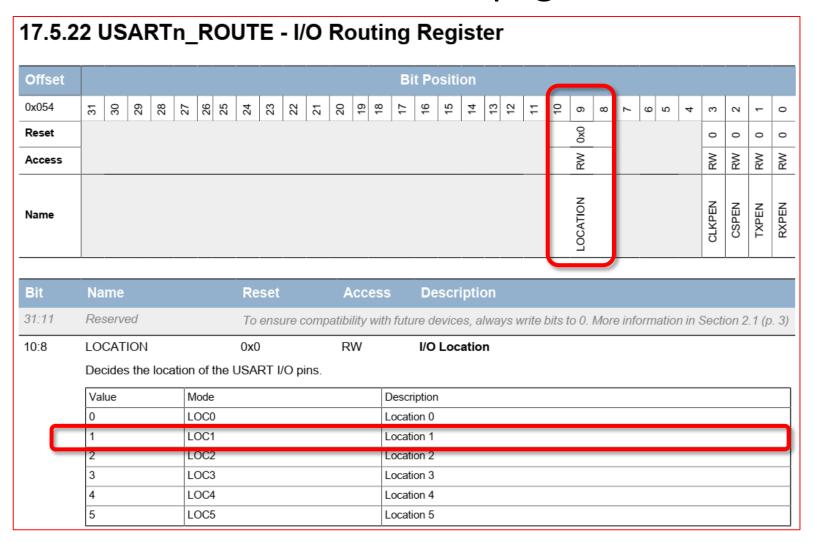

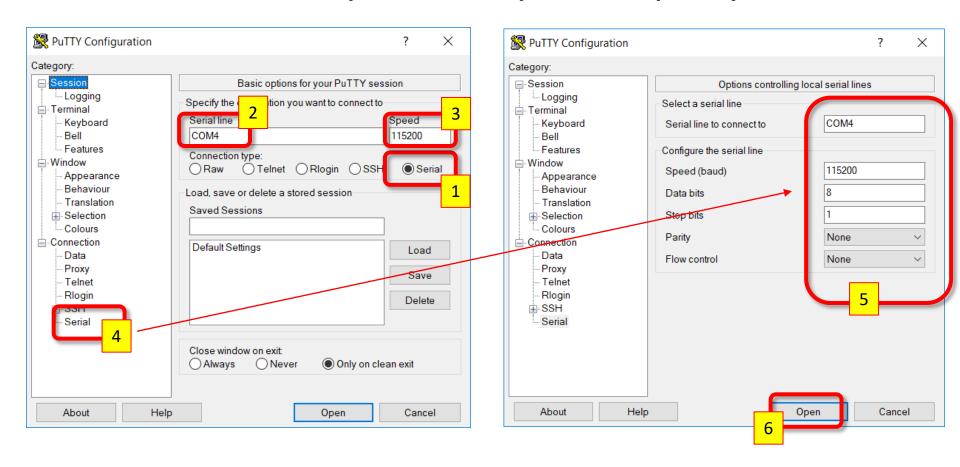

The BSP use EFM32 peripheral UART0, Location 1 (TX pin PE0, RX pin PE1) on baudrate 115200-8-N-1 to communicate with the board controller.

#### Note

The BSP is only functional when the Starter Kit is USB-powered, using these function calls with USB disconnected will give unpredictable results.

Refer to page 14 of 01\_EFM32\_User\_guide\_efm32gg-stk3700-user\_guide.pdf

#### UART connection on uC

#### Checking the schematic

MCU\_PE[15..0] >>

Port F (PF) connections:

Port E (PE) connections:

MCU\_PF[12..5] >> MCU PF7

**Enabling UART:**

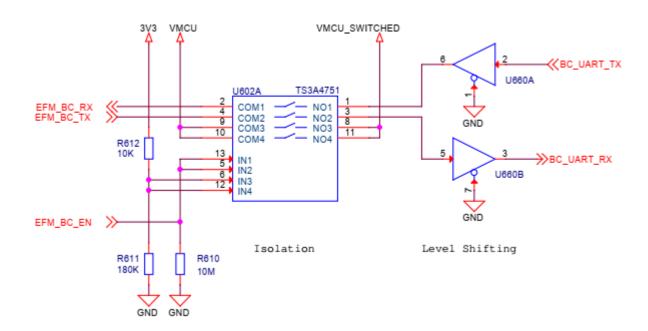

#### UART connection — Board Controller

#### UART connection — Board Controller

#### **Board Controller:**

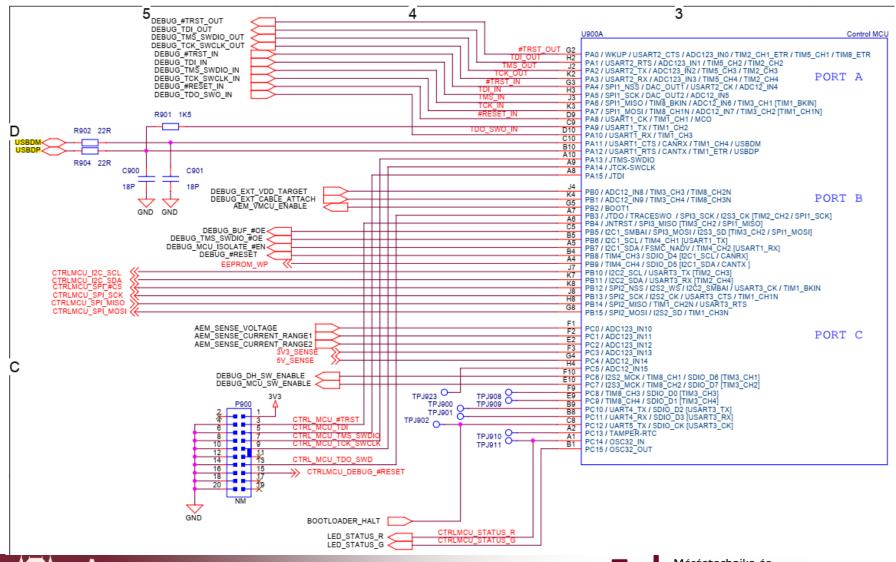

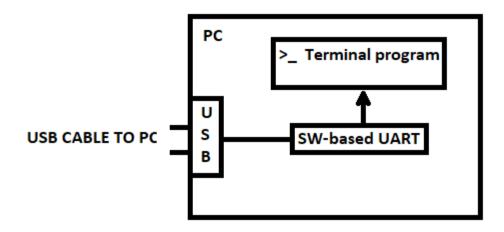

#### **UART** connection – USB PHY

USB:

#### UART connection – Block diagram

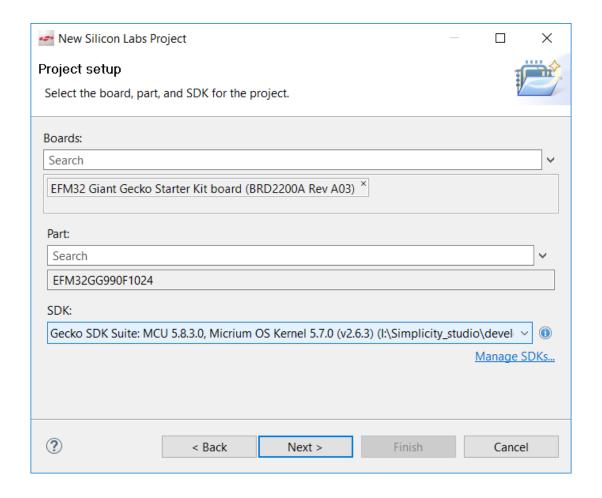

## Strating with a new project

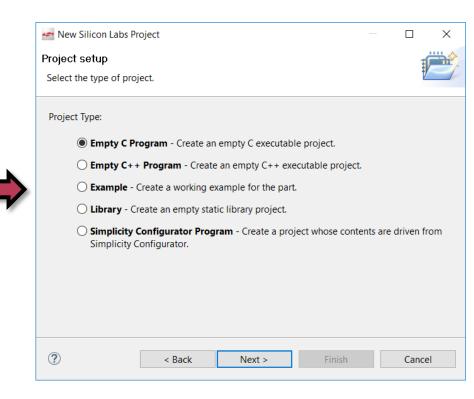

File->New->Project->Silicon Labs MCU Project:

#### Strating with a new project

File->New->Project->Silicon Labs MCU Project:

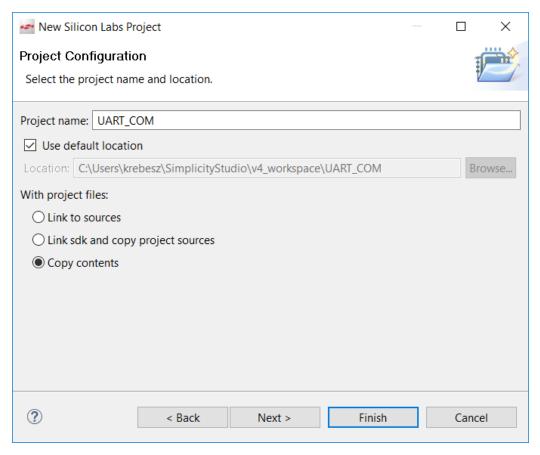

## Strating with a new project

• Give project name and location, and set Copy content:

## Project created – start programming

- Main.c can be also renamed to UART\_COM.c

- Although an empty C project has been created a program skeleton is offered automaticly

```

Project Explorer 🛭

■ UART_COM.c 器

#include "em device.h"

STK3700_blink [GNU ARM v7.2.1 - Debug] [EFM32GG990F1024 - (

#include "em chip.h"

STK3700_button [GNU ARM v7.2.1 - Debug] [EFM32GG990F1024]

3

UART_COM [GNU ARM v7.2.1 - Debug] [EFM32GG990F1024 - Geo

4⊖int main(void)

> 🛍 Includes

> CMSIS

/* Chip errata */

> 🗁 emlib

CHIP Init();

/* Infinite loop */

DART_COM.c

while (1) {

12

13

```

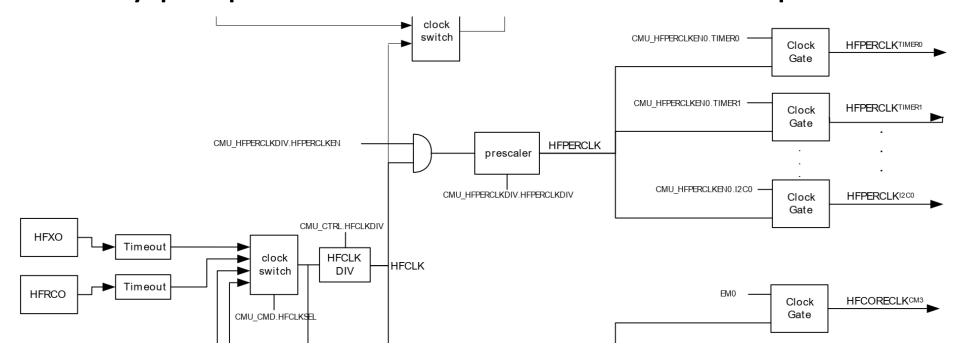

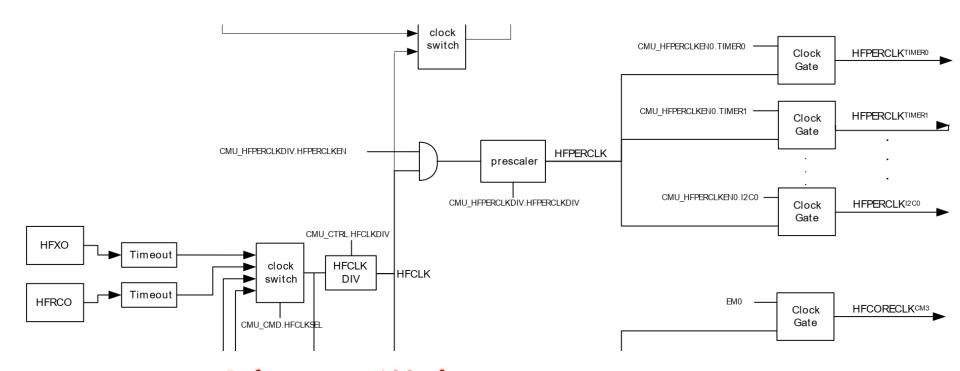

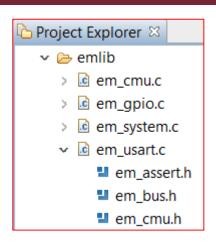

## CLK for GPIO peripheral (CMU system)

Every peripheral has and needs a CLK to operate

Refer to page 128 of 03\_EFM32\_Reference\_manual\_EFM32GG-reference\_manual.pdf

## CLK for GPIO peripheral

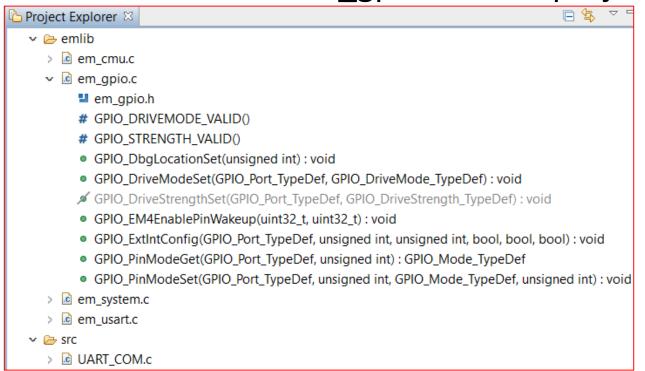

- CLK for GPIO peripheral must be enabled

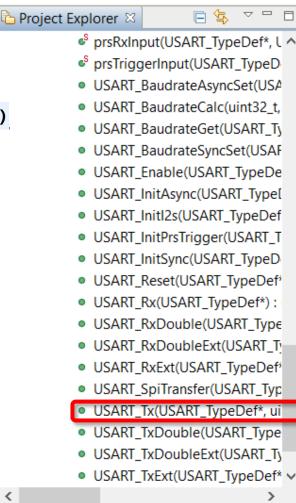

- Search the library where Simplicity Studio is installed

- O Contains include (inc: \*.c) and source (src: \*.h) files: i:\Simplicity\_studio\developer\sdks\gecko\_sdk\_suite\v2.6\platform\emlib\

- Following files has to be drag-and-dropped into emlib library of the project (see next slide):

- em\_cmu.c (clock management unit)

- o em\_gpio.c

- o em\_usart.c

#### CLK for GPIO peripheral

Furthermore they have to be included into the program:

```

Project Explorer

□

#include "en device.h"

STK3700_blink [GNU ARM v7.2.1 - Debug] [EFM32GG990F1024 - (

#include "em chip.h"

STK3700_button [GNU ARM v7.2.1 - Debug] [EFM32GG990F1024

#include "em cmu.h"

✓ MART_COM [GNU ARM v7.2.1 - Debug] [EFM32GG990F1024 - Ged]

#include "em gpio.h"

> includes

#include "em usart.h"

> B CMSIS

emlib

em_cmu.c

9⊖int main(void)

em_gpio.c

10

em_system.c

/* Chip errata */

em_usart.c

CHIP Init();

Src

DART_COM.c.

/* Infinite loop */

while (1) {

```

Check how the CLK for GPIO can be enabled:

- In programming window click on em device.h and press F3 -> em device.h opens

- Defines for different processors from EFM32 family are found -> search for your own type

(EFM32GG990F1024):

```

*UART_COM.c

🛅 em device.h 🔀

t defined(EFM32GG942FT024)

#include "efm32gg942f1024.h"

149

#elif defined(EFM32GG942F512)

#include "efm32gg942f512.h"

152

#elif defined(EFM32GG980F1024)

#include "efm32gg980f1024.h"

155

#elif defined(EFM32GG980F512)

#include "efm32gg980f512.h"

158

#elif defined(EFM32GG990F1024)

```

- Click on EFM32GG990F1024.h and press F3

- EFM32GG990F1024.h contains (among others)

- o IT number that belongs to a certain peripheral

Memory addresses, e.g. base addresses

- No need to check reference manual for e.g. base addresses

- Refer to page 17 of

03\_EFM32\_Reference\_manual\_EFM32GG-reference\_manual.pdf to

base addresses

Defines types that are pointers for the base address

```

410 #define CMU ((CMU_TypeDef *) CMU_BASE) /**< CMU base pointer */

411 #define GPIO ((GPIO_TypeDef *) GPIO_BASE) /**< GPIO base pointer */

```

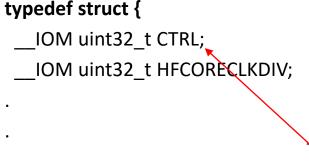

- Click on (CMU\_TypeDef \*) and press F3

- Type definition of CMU pops-up in efm32gg\_cmu.h which is a structure

- Elegant solution

CMU\_TypeDef;

| 0400-0400                |     |

|--------------------------|-----|

| 0x400e0400<br>0x400e0000 | AES |

| 0x400cc400               |     |

| 0x400cc000               | PRS |

| 0x400ca400               | RMU |

| 0x400ca000               | KMO |

| 0x400c8400               | CMU |

| 0x400c8000<br>0x400c6400 |     |

| 0x400c6400               | EMU |

| 0.40000000               |     |

The offset register address is relative to the registers base address.

| Offset | Name             | Туре | Description                                 |

|--------|------------------|------|---------------------------------------------|

| 0x000  | CMU_CTRL         | RW   | CMU Control Register                        |

| 0x004  | CMU_HFCORECLKDIV | RW   | High Frequency Core Clock Division Register |

Elements of structure is assigned to the memory registers via base-address pointer!

In the header file:

In the RM see p.136 (03\_EFM32\_Reference\_manual\_EFM32GG-reference\_manual.pdf):

| iii tile neader me.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             | the min see p. 15 | o (os_Envisz_Nererence_manda | _   | oo reference_manaan.parj.                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------|------------------------------|-----|-----------------------------------------------------|

| typedef struct {                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>,</b>    | 0x000             | CMU_CTRL                     | RW  | CMU Control Register                                |

| IOM uint32_t CTRL;<br>IOM uint32 t HFCORECLKDIV;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             | 0x004             | CMU_HFCORECLKDIV             | RW  | High Frequency Core Clock Division Register         |

| IOM uint32_t HFPERCLKDIV;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Z.          | 0x008             | CMU_HFPERCLKDIV              | RW  | High Frequency Peripheral Clock Division Register   |

| IOM uint32_t HFRCOCTRL;<br>IOM uint32 t LFRCOCTRL;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7           | 0x00C             | CMU_HFRCOCTRL                | RW  | HFRCO Control Register                              |

| IOM uint32 t AUXHFRCOCTRL;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | In l        | 0x010             | CMU_LFRCOCTRL                | RW  | LFRCO Control Register                              |

| IOM uint32_t CALCTRL;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             | 0x014             | CMU_AUXHFRCOCTRL             | RW  | AUXHFRCO Control Register                           |

| IOM uint32_t CALCNT;<br>_IOM uint32 t OSCENCMD;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | 0x018             | CMU_CALCTRL                  | RW  | Calibration Control Register                        |

| IOM uint32_t CMD;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             | 0x01C             | CMU_CALCNT                   | RWH | Calibration Counter Register                        |

| IOM uint32_t LFCLKSEL;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>a.</b> I | 0x020             | CMU_OSCENCMD                 | W1  | Oscillator Enable/Disable Command Register          |

| IM uint32_t STATUS;<br>_IM uint32 t IF;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             | 0x024             | CMU_CMD                      | W1  | Command Register                                    |

| IOM uint32_t IFS;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2           | 0x028             | CMU_LFCLKSEL                 | RW  | Low Frequency Clock Select Register                 |

| IOM uint32_t IFC;<br>IOM uint32 t IEN;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9           | 0x02C             | CMU_STATUS                   | R   | Status Register                                     |

| IOM uint32_t HFCORECLKEN0;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | e           | 0x030             | CMU_IF                       | R   | Interrupt Flag Register                             |

| IOM uint32_t HFPERCLKEN0;<br>uint32 t RESERVED0[2U];                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -0          | 0x034             | CMU_IFS                      | W1  | Interrupt Flag Set Register                         |

| <pre>uint32_t RESERVED0[2U]; IM uint32 t SYNCBUSY;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Δ           | 0x038             | CMU_IFC                      | W1  | Interrupt Flag Clear Register                       |

| IOM uint32_t FREEZE;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>14</b>   | 0x03C             | CMU_IEN                      | RW  | Interrupt Enable Register                           |

| IOM uint32_t LFACLKEN0;<br>uint32 t RESERVED1[1U];                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2           | 0x040             | CMU_HFCORECLKEN0             | RW  | High Frequency Core Clock Enable Register 0         |

| IOM uint32_t LFBCLKEN0;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>/</b> R  | 0x044             | CMU_HFPERCLKEN0              | RW  | High Frequency Peripheral Clock Enable Register 0   |

| uint32 t RESERVED2[1U];                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             | 0x050             | CMU_SYNCBUSY                 | R   | Synchronization Busy Register                       |

| IOM uint32 t LFAPRESCO;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             | 0x054             | CMU_FREEZE                   | RW  | Freeze Register                                     |

| uint32_t RESERVED3[1U];                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             | 0x058             | CMU_LFACLKEN0                | RW  | Low Frequency A Clock Enable Register 0 (Async Reg) |

| IOM uint32_t LFBPRESC0;<br>uint32 t RESERVED4[1U];                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             | 0x060             | CMU_LFBCLKEN0                | RW  | Low Frequency B Clock Enable Register 0 (Async Reg) |

| IOM uint32_t PCNTCTRL;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             | 0x068             | CMU_LFAPRESC0                | RW  | Low Frequency A Prescaler Register 0 (Async Reg)    |

| IOM uint32_t LCDCTRL;<br>IOM uint32 t ROUTE;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             | 0x070             | CMU_LFBPRESC0                | RW  | Low Frequency B Prescaler Register 0 (Async Reg)    |

| IOM uint32_t ROUTE,<br>IOM uint32_t LOCK;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             | 0x078             | CMU_PCNTCTRL                 | RW  | PCNT Control Register                               |

| } CMU_TypeDef;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             | 0x07C             | CMU_LCDCTRL                  | RW  | LCD Control Register                                |

| / <u>.</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             | 0x080             | CMU_ROUTE                    | RW  | I/O Routing Register                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | 0x084             | CMU_LOCK                     | RW  | Configuration Lock Register                         |

| COMMUNICATION TO COMMUN |             |                   |                              |     |                                                     |

#### CLK for GPIO peripheral

- Using the structure CMU

- OCMU is a structure pointer: arrow is used ->

- CMU-> (Ctrl+Space will complement)

- Needed: HFPERCLKENO (Bit 13 is used for GPIO CLK)

| 11.5.18 CMU_HFPERCLKEN0 - High Frequency Peripheral Clock Enable Register 0 See ref.man. P150: |                                                                                                                                                    |  |  |  |  |  |  |  |  |    |    |    |         |    |      |      |         |      |         |      |      |       |       |        |        |        |        |       |       |        |        |        |

|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|----|----|----|---------|----|------|------|---------|------|---------|------|------|-------|-------|--------|--------|--------|--------|-------|-------|--------|--------|--------|

| Offset                                                                                         | Bit Position                                                                                                                                       |  |  |  |  |  |  |  |  |    |    |    |         |    |      |      |         |      |         |      |      |       |       |        |        |        |        |       |       |        |        |        |

| 0x044                                                                                          | 31<br>30<br>30<br>27<br>28<br>29<br>29<br>29<br>20<br>20<br>20<br>21<br>40<br>40<br>40<br>40<br>40<br>40<br>40<br>40<br>40<br>40<br>40<br>40<br>40 |  |  |  |  |  |  |  |  | 18 | 17 | 16 | 15      | 4  | 13   | 12   | 1       | 10   | 6       | œ    | 7    | 9     | 2     | 4      | က      | 2      | -      | 0     |       |        |        |        |

| Reset                                                                                          |                                                                                                                                                    |  |  |  |  |  |  |  |  |    | 0  | 0  | 0       | 0  | 0    | 0    | 0       | 0    | 0       | 0    | 0    | 0     | 0     | 0      | 0      | 0      | 0      | 0     |       |        |        |        |

| Access                                                                                         |                                                                                                                                                    |  |  |  |  |  |  |  |  |    |    | RW | RW<br>W | W. | RW   | RW   | RW<br>W | RW   | RW<br>W | RW   | RW   | RW    | RW    | RW     | RW     | RW     | RW     | RW    | RW    |        |        |        |

| Name                                                                                           |                                                                                                                                                    |  |  |  |  |  |  |  |  |    |    |    |         |    | DAC0 | ADC0 | PRS     | VCMP | GPIO    | 12C1 | 12C0 | ACMP1 | ACMP0 | TIMER3 | TIMER2 | TIMER1 | TIMER0 | UART1 | UART0 | USART2 | USART1 | USARTO |

• A define is available for Bit 13 in efm32gg cmu.h

919 #define CMU HFPERCLKEN0 GPIO

(0x1UL << 13)

## CLK for GPIO peripheral (CMU system)

Every peripheral has and needs a CLK to operate

Refer to page 128 of 03\_EFM32\_Reference\_manual\_EFM32GG-reference\_manual.pdf

Code to be used:

CMU->HFPERCLKENO |= CMU\_HFPERCLKENO\_GPIO;

- Remember: PF7=1 has to be set

- More elegant approach if a function can be found for a problem -> Results in more readable code

- Check functions under em\_gpio.c in the project

27.slide

- Open (double click on) GPIO\_PinModeSet

- o em\_gpio.c opens at the function implementation

- Remark: em\_gpio.h also contains the definition of functions and even more, e.g. static functions available only in header files

- Note: these functions are independent of the type of processor, since the processor dependent specialities are defined in efm32gg\_xxx.h

- Helps to develop portable code that is compatible with other processors (from the same processor family at least)