# Embedded and ambient systems 2024.09.18.

### **Practice 3**

### Peripheral handling at register level

Méréstechnika és Információs Rendszerek Tanszék

Budapest University of Technology and Economics Department of Measurement and Information Systems

© BME-MIT

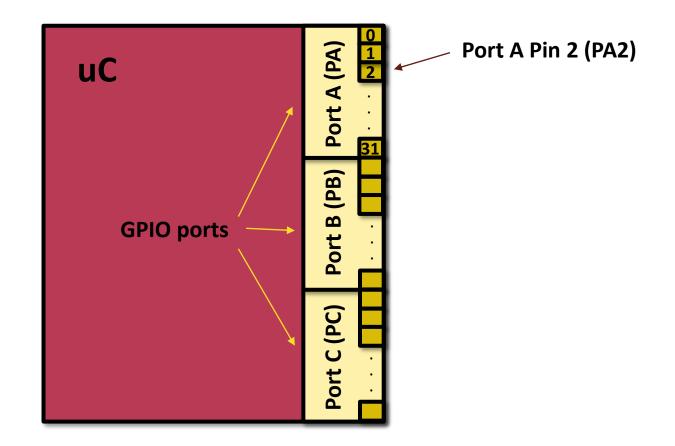

### 1) Peripheral handling at low level

- Useful to see how peripherals work at a register level (hidden by the high-level functions)

- See the LED-blinking-by-button project built up from empty code at a low level

- Source files needed:

- o EFM32GG-BRD2200A-A03-schematic.pdf

- Board schematic: peripherals and their interconnection

- o EFM32GG-RM.pdf (RM=reference manual)

- Use it as a reference, i.e., the necessary chapters are needed only to be read

- It is a good way to understand general topics, e.g., communication (e.g. UART) used by the uC

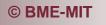

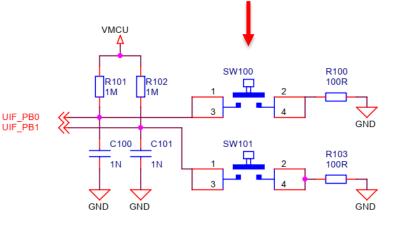

### 1) Physical connections on the board

- Find the connections between the uC and the buttons based on the schematic

- Buttons: connected to 'Port B' of GPIO peripheral

UIF\_PBO -> MCU\_PB9

UIF\_PB1 -> MCU\_PB10

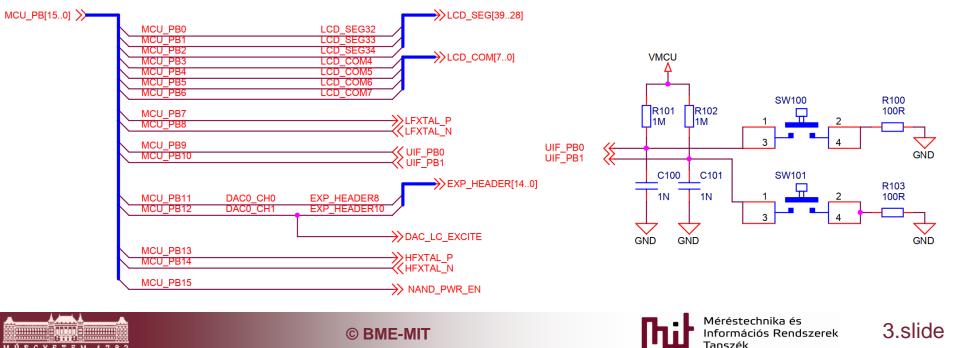

### 1) Physical connections on the board

- Find the connections between the uC and the LEDs based on the schematic

- LEDs: connected to 'Port E' of GPIO

UIF\_LED0 -> MCU\_PE2

UIF\_LED1 -> MCU\_PE3

UIF\_LED1.01

© BME-MIT

Méréstechnika és

Tanszék

Információs Rendszerek

### 1) Physical connections on the board

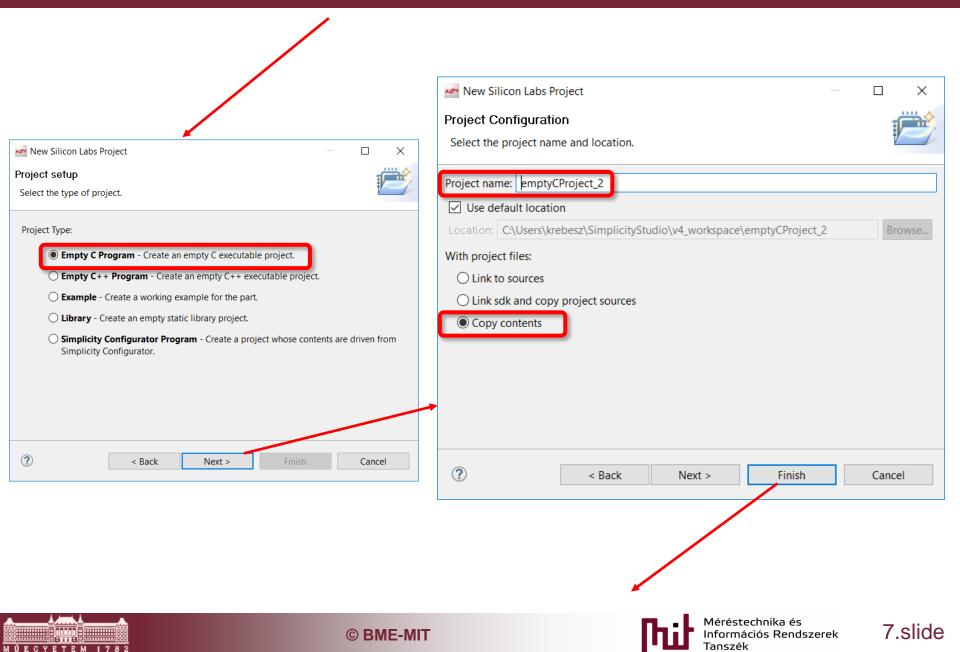

### 2) Start a new empty project

#### File->New->Project:

мÚ

| - 🗆                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 🗙 🔤 New Silicon Labs Project                                                                                                                       | – 🗆 X                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Select a wizard<br>Create a C/C++/Assembly project targeting Silicon Labs MCUs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Project setup<br>Select the board, part, and SDK for the project                                                                                   | t.                                                                                                     |

| Wizards:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Boards:<br>EFM32 Giant Gecko Starter Kit board (BRD22<br>Part:<br>Search<br>EFM32GG990F1024<br>SDK:<br>Gecko SDK Suite: MCU 5.8.3.0, Micrium OS Ke | v<br>200A Rev A03) ×<br>v<br>ernel 5.7.0 (v2.6.3) (I:\Simplicity_studio\devel v)<br><u>Manage SDKs</u> |

| Image: Sector | ? < Back                                                                                                                                           | Next > Finish Cancel                                                                                   |

| © BME-MIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                    | Néréstechnika és<br>nformációs Rendszerek 6.Slide                                                      |

### 3) Start a new empty project

### 3) Empty project created

Simplicity IDE - emptyCProject\_2/src/main.c - Simplicity Studio ™

File Edit Source Refactor Navigate Search Project Run Window Help

#### \* ▼ 🗣 ▼ 🗁 ▼ 🔚 🐚 | 🗞 ▼ 🗞 ▼ 🖢 ▼ 🖓 ▼ 🏷 → 🔿 ▼ 🕮

| င်္ခ Project Explorer 🛛                                   | 🖻 🔄 🏹 🗖 🗖 🚺 main.c 🛛                                                |

|-----------------------------------------------------------|---------------------------------------------------------------------|

| ✓ <sup>Imest</sup> emptyCProject_2 [GNU ARM v7.2.1 - Debu | g] [EFM32GG990F1024 - Gecko SDK Sui 1 <b>#include</b> "em_device.h" |

| > 🔊 Includes                                              | 2 <b>#include</b> "em_chip.h"                                       |

| > 🗁 CMSIS                                                 | 3                                                                   |

| > 🗁 emlib                                                 | 4⊖int main(void)<br>5 {                                             |

| 🗸 🗁 src                                                   | 6 /* Chip errata */                                                 |

| > 🖻 main.c                                                | 7 CHIP_Init();                                                      |

|                                                           | 8                                                                   |

|                                                           | 9 /* Infinite loop */                                               |

|                                                           | 10 while (1) {                                                      |

|                                                           | 11 }                                                                |

|                                                           | 12 }                                                                |

|                                                           | 13                                                                  |

|                                                           |                                                                     |

|                                                           |                                                                     |

#### Comment out CHIP\_Init(); function

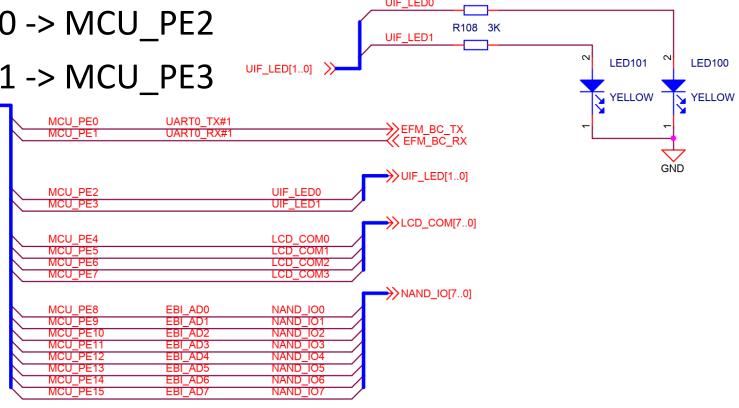

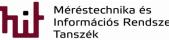

### 4) Get to know necessary peripherals

- Two peripherals are needed

General Purpose Input Output (GPIO)

Clock Management Unit (CMU)

- Check p.17 Fig.5.2 of EFM32GG-RM.pdf

- Memory map of the system

- 32-bit uC -> 4GB addressable memory theoretically but only a small part is physically available

- Obviously only the physically available amount of memory is shown in the map

- (see next slide for the map)

### 4) Memory map (full)

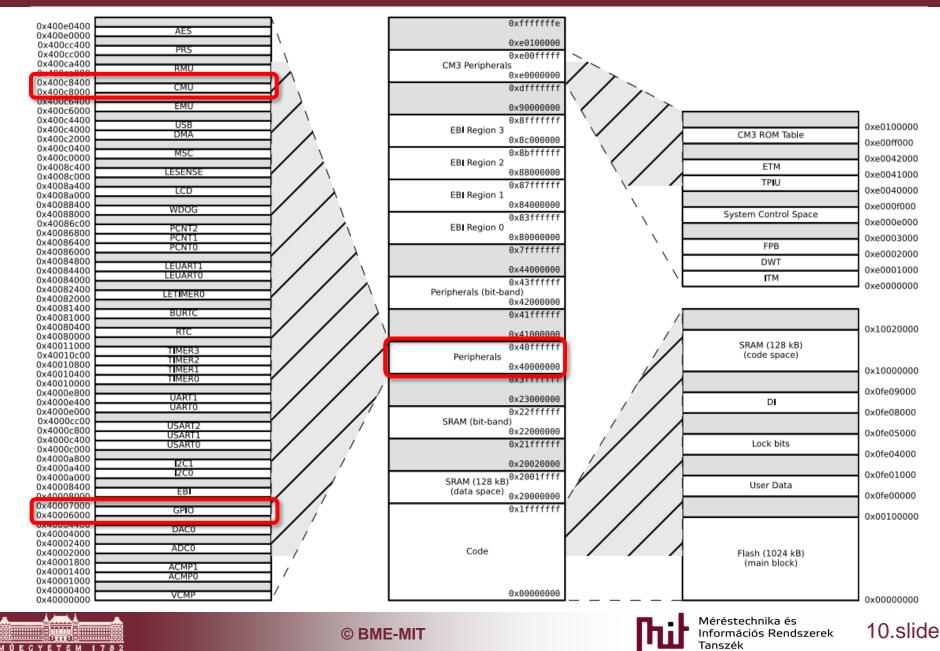

## 4) Memory map (CMU and GPIO regs.)

- The address space is important

- Starts from bottom and increasing to the top

- Base addresses of peripheral registers have to be determined

- CMU base address: 0x400c8000

- GPIO base address: 0x40006000

| 0x400c8400 | СМО                    |          |

|------------|------------------------|----------|

| 0x400c8000 | СМО                    |          |

| 0X400C0400 | EMU                    |          |

| 0x400c6000 | ENO                    |          |

| 0x400c4400 | USB                    |          |

| 0x400c4000 | DMA                    |          |

| 0x400c2000 | DINA                   |          |

| 0x400c0400 | MSC                    |          |

| 0x400c0000 | 1150                   |          |

| 0x4008c400 | LESENSE                |          |

| 0x4008c000 | LEGENGE                |          |

| 0x4008a400 | LCD                    |          |

| 0x4008a000 | 200                    |          |

| 0x40088400 | WDOG                   |          |

| 0x40088000 | 11000                  | Y        |

| 0x40086c00 | PCNT2                  |          |

| 0x40086800 | PCNT1                  |          |

| 0x40086400 | PCNTO                  |          |

| 0x40086000 |                        |          |

| 0x40084800 | LEUART1                |          |

| 0x40084400 | LEUARTO                |          |

| 0x40084000 | LEGARTO                |          |

| 0x40082400 | LETIMERO               | i        |

| 0x40082000 | Letimento              |          |

| 0x40081400 | BURTC                  |          |

| 0x40081000 | bollic                 |          |

| 0x40080400 | RTC                    |          |

| 0x40080000 | Ric                    | /        |

| 0x40011000 | TIMER3                 |          |

| 0x40010c00 | TIMER2                 |          |

| 0x40010800 | TIMER1                 |          |

| 0x40010400 | TIMERO                 |          |

| 0x40010000 | THERE                  |          |

| 0x4000e800 | UART1                  |          |

| 0x4000e400 | UARTO                  |          |

| 0x4000e000 | - OAIGO                |          |

| 0x4000cc00 | USART2                 | r        |

| 0x4000c800 | USARTI                 |          |

| 0x4000c400 | USARTO                 |          |

| 0x4000c000 | USANO                  |          |

| 0x4000a800 | 2C1                    |          |

| 0x4000a400 | 201                    |          |

| 0x4000a000 | 200                    |          |

| 0x40008400 | EBI                    |          |

| 0×40008000 |                        |          |

| 0x40007000 | GPIO                   |          |

| 0x40006000 | 610                    |          |

|            | Méréstechnika és       | 4.4      |

| Init       | Információs Rendszerek | 11.slide |

Tanszék

### 5) Base address aliases in code

Avoid memorizing memory addresses using aliases in the code (use <u>Tab</u> instead of Space)

```

🖻 main.c 🖾

1 #include "em device.h"

#include "em chip.h"

3

#define CMU BASE ADDR

0x400c8000

#define GPIO BASE ADDR 0x40006000

6

7⊖int main(void)

8

/* Chip errata */

9

//CHIP Init();

10

11

12

/* Infinite loop */

13

while (1) {

14

15 }

16

```

### 6) Accessing registers using base addr.

- Base address is only the start address of a certain kind of register array, like CMU registers

- To access a specific register (e.g. register for REG\_A of a register array) an offset address have to be used relative to the base address

- The address of a specific register is the base + offset address

- e.g. REG\_A -> 0x400c8000+0x044

- Note, that registers usually contain configuration bits to be set (see later)

### 6) Explanation for setting reg. content

- 32-bit registers are addressed

- Memory address is determined to store data there

- Remember: base address + offset = memory address

- Problem: this is a number for the compiler not an address

- Solution: to turn this number into a memory address it has to be converted into a **pointer** (use \* to mark a pointer)

- In C, pointer is a variable type that points to a certain part of the memory (to a memory address where e.g. a register store data)

- Turning a number into a pointer means forcing the change of variable type, called **cast**ing

- The way to refer to a certain register is uC dependent, its implementation has to be checked via examples, description, manual, etc.

### 6) Explanation for setting reg. content

#### In our case a pointer can be given by:

- (\*(volatile long unsigned int \*)(0x400c8000+0x044))

- First \*: a value is to be written into the memory (register) at the given address

- volatile: avoid to be optimized out

- long unsigned int: type of the pointer (note: 32-bit reg.)

- Second \*: this is a pointer

- 0x400c8000+0x044 : this is the known memory address

- The pointer itself:

- (volatile long unsigned int \*)(0x400c8000+0x044)

- To give a value for this pointer the first \* is used

### 6) Explanation for setting reg. content

- Useful to make it more structured looking

- #define REG\_A (\*(volatile long unsigned int \*)(0x400c8000+0x044))

- Setting a bit, e.g., set Bit13

- REG\_A |=1<<13

- |= : bitwise OR used for setting a bit

- bbbbbbb |= 00100000 results bb1bbbb where b is either 0 or 1

- Clearing a bit, e.g., clear Bit13

- REG\_A &=~(1<<13)

- &=~ : bitwise AND of inverted values used for clearing

- bbbbbbb &=~ 00100000 -> bbbbbbbb &= 11011111

bb0bbbbb

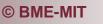

#### Check p.128 Fig.11.1 of EFM32GG-RM.pdf

- Clock distribution network is shown

- Clock has to be provided for the peripherals

- This is uC dependent but always has to be take care of providing CLK for the peripherals and enabling the peripherals

- Find HFRCO: high-frequency RC osc

- Not too much precise but readily available -> no external CLK source is needed

Check the signal path toward the GPIO peripheral

- Check p.136 of EFM32GG-RM.pdf

- Registers of CMU peripheral are shown with brief description

- Register addresses are given relative to the base address

- E.g. CMU\_CTRL addr: from 0x000 to the next register starting 0x004, which is 4bytes, i.e. 32 bits

The offset register address is relative to the registers base address.

| Offset | Name             | Туре | Description                                        |

|--------|------------------|------|----------------------------------------------------|

| 0x000  | CMU_CTRL         | RW   | CMU Control Register                               |

| 0x004  | CMU_HFCORECLKDIV | RW   | High Frequency Core Clock Division Register        |

| 0x008  | CMU_HFPERCLKDIV  | RW   | High Frequency Peripheral Clock Division Register  |

| 0x00C  | CMU_HFRCOCTRL    | RW   | HFRCO Control Register                             |

| 0x010  | CMU_LFRCOCTRL    | RW   | LFRCO Control Register                             |

|        | © BME-MIT        | 1    | Méréstechnika és<br>Információs Rendszerek 19.Slid |

# Use copy-paste to put the register addresses into the code

- 0x008 CMU\_HFPERCLKDIV\_OFFS

- 0x044 CMU\_HFPERCLKEN0\_OFFS

The offset register address is relative to the registers base address.

| Offset | Name             | Туре | Description                                       |

|--------|------------------|------|---------------------------------------------------|

| 0x000  | CMU_CTRL         | RW   | CMU Control Register                              |

| 0x004  | CMU_HFCORECLKDIV | RW   | High Frequency Core Clock Division Register       |

| 0x008  | CMU_HFPERCLKDIV  | RW   | High Frequency Peripheral Clock Division Register |

| 0x00C  | CMU_HFRCOCTRL    | RW   | HFRCO Control Register                            |

| 0x010  | CMU_LFRCOCTRL    | RW   | LFRCO Control Register                            |

|        |                  |      |                                                   |

- Check p.137 of EFM32GG-RM.pdf

- Bit-level description of CMU registers

- Check default values: values after Reset

- 11.5.1 CMU\_CTRL CMU Control Register

| Offset |      | ·     |     |        |      |     |     | -          |      |      |            |      |    |             | Bi         | t Po   | ositi    | on     |           |        |        |      |             |     |                 |    |            |   |           |   |          |     |

|--------|------|-------|-----|--------|------|-----|-----|------------|------|------|------------|------|----|-------------|------------|--------|----------|--------|-----------|--------|--------|------|-------------|-----|-----------------|----|------------|---|-----------|---|----------|-----|

| 0x000  | 31   | 30    | 29  | 28     | 27   | 26  | 25  | 24         | 23   | 22   | 21         | 20   | 19 | 18          | 17         | 16     | 15       | 14     | 13        | 12     | 1      | 10   | 6           | 8   | 7               | 9  | 5          | 4 | ю         | 2 | -        | 0   |

| Reset  |      | 0     |     | 0      |      |     |     | 0×0        |      |      | 0×0        |      |    | 0x3         | 0          |        | 0×0      |        | 0         | ç      | nxn    | 0    | 0X3         |     | 0               | 50 | 1XU        |   | 0x3       |   | 0~0      | 222 |

| Access |      | RW    |     | RW     |      |     |     | RW         |      |      | RW         |      | I  | RW          | RW         |        | RW       |        | RW        | Ì      |        |      | 2<br>2<br>2 |     | RW              |    | ۶<br>۲     |   | RW        |   | MA<br>MA |     |

| Name   |      | HFLE  |     | DBGCLK |      |     |     | CLKOUTSEL1 |      |      | CLKOUTSELO |      |    | LFXOTIMEOUT | LFXOBUFCUR |        | HFCLKDIV |        | LFXOBOOST |        |        |      | HFXUIIMEUUI |     | HFXOGLITCHDETEN |    | HFXOBUFCUK |   | HEXOROOST |   | HEXOMODE | 1   |

| Bit    | Na   | me    |     |        |      |     |     | Re         | set  |      |            | A    | CC | cess        |            | De     | scr      | iptio  | on        |        |        |      |             |     |                 |    |            |   |           |   |          |     |

| 22:20  | CLK  | (OU   | TSE | L0     |      |     |     | 0x0        | )    |      |            | R    | W  |             |            | Clo    | ock (    | Outp   | out       | Sel    | ect (  | )    |             |     |                 |    |            |   |           |   |          |     |

|        | Con  | trols | the | cloc   | k ou | tpu | t m | ultipl     | exer | : To | actu       | ally | ou | tput (      | on th      | ne pi  | n, se    | et CL  | KC        | DUT    | 0PE    | N in | СМ          | J_R | OUT             | E. |            |   |           |   |          |     |

|        | Valu | Je    |     |        | M    | ode |     |            |      |      |            |      |    |             | )escr      | iptior | ı        |        |           |        |        |      |             |     |                 |    |            |   |           |   |          |     |

|        | 0    |       |     |        | HF   | RC  | 0   |            |      |      |            |      |    | H           | IFRC       | CO (d  | irectl   | y froi | m o       | scilla | itor). |      |             |     |                 |    |            |   |           |   |          |     |

|        |      | _     |     |        |      |     |     |            |      |      |            |      |    |             |            |        |          |        |           |        |        |      |             |     |                 |    |            |   | a óc      |   |          |     |

stechnika és nációs Rendszerek

- Check p.140 of EFM32GG-RM.pdf

- Enable CLK

11.5.3 CMU\_HFPERCLKDIV - High Frequency Peripheral Clock Division Register

| Offset |    |       |     |    |    |    |    |    |      |       |     |        |       |      | Bi   | t Po  | siti | on    |      |       |       |      |       |            |       |      |       |        |       |             |       |    |

|--------|----|-------|-----|----|----|----|----|----|------|-------|-----|--------|-------|------|------|-------|------|-------|------|-------|-------|------|-------|------------|-------|------|-------|--------|-------|-------------|-------|----|

| 0x008  | 31 | 30    | 29  | 28 | 27 | 26 | 25 | 24 | 23   | 22    | 21  | 20     | 19    | 18   | 17   | 16    | 15   | 14    | 13   | 12    | 5     | 10   | 6     | 80         | 2     | 9    | 5     | 4      | e     | 2           | -     | 0  |

| Reset  |    |       |     |    |    |    |    |    |      |       |     |        |       |      |      |       |      |       |      |       |       |      |       | -          |       |      |       |        |       | 0x0         |       |    |

| Access |    |       |     |    |    |    |    |    |      |       |     |        |       |      |      |       |      |       |      |       |       |      |       | RV         |       |      |       |        |       | RW          |       |    |

| Name   |    |       |     |    |    |    |    |    |      |       |     |        |       |      |      |       |      |       |      |       |       |      |       | HFPERCLKEN |       |      |       |        |       | HFPERCLKDIV |       |    |

| Bit    | Na | me    |     |    |    |    |    | Re | set  |       |     | A      | ссе   | ss   |      | De    | scri | ipti  | on   |       |       |      |       |            |       |      |       |        |       |             |       |    |

| 31:9   | Re | serve | ed  |    |    |    |    | То | ensu | re co | mpa | atibil | ity n | vith | futu | re de | vice | əs, a | lwa  | iys n | vrite | bits | to 0. | More       | e int | form | atior | n in S | Secti | on 2.       | 1 (p. | 3) |

| 8      | HF | PER   | CLK | EN |    |    |    | 1  |      |       |     | R۷     | N     |      |      | HFI   | PER  | CL    | < Er | nabl  | е     |      |       |            |       |      |       |        |       |             |       |    |

Set to enable the HFPERCLK.

#### Check p.150 of EFM32GG-RM.pdf

#### Enable CLK for GPIO

#### 11.5.18 CMU\_HFPERCLKEN0 - High Frequency Peripheral Clock Enable Register 0

| Offset |    |                                                    |      |        |       |     |       |      |      |    |    |    |     |      | Bi   | t Po | ositi | on   |      | 1    |      |       |       |        |        |        |        |       |       |        |        |        |

|--------|----|----------------------------------------------------|------|--------|-------|-----|-------|------|------|----|----|----|-----|------|------|------|-------|------|------|------|------|-------|-------|--------|--------|--------|--------|-------|-------|--------|--------|--------|

| 0x044  | 31 | 30                                                 | 29   | 28     | 27    | 26  | 25    | 24   | 23   | 22 | 21 | 20 | 19  | 18   | 17   | 16   | 15    | 14   | 13   | 12   | 5    | 10    | 6     | 8      | 7      | 9      | 5      | 4     | с     | 2      | -      | 0      |

| Reset  |    |                                                    |      |        |       |     |       |      |      |    |    |    |     |      | 0    | 0    | 0     | 0    | 0    | 0    | 0    | 0     | 0     | 0      | 0      | 0      | 0      | 0     | 0     | 0      | 0      | 0      |

| Access |    |                                                    |      |        |       |     |       |      |      |    |    |    |     |      | RW   | RW   | RV    | RV   | RW   | RW   | RW   | RV    | RW    | RW     | RW     | RV     | RW     | RW    | RV    | RV     | RW     | RV     |

| Name   |    |                                                    |      |        | _     |     |       |      |      |    |    |    |     |      | DACO | ADC0 | PRS   | VCMP | GPIO | 12C1 | 12C0 | ACMP1 | ACMP0 | TIMER3 | TIMER2 | TIMER1 | TIMERO | UART1 | UARTO | USART2 | USART1 | USARTO |

| Bit    | Na | ame                                                |      |        |       |     |       | Re   | eset |    |    | A  | ٩cc | cess | •    | De   | scr   | ipti | on   |      |      |       |       |        |        |        |        |       |       |        |        |        |

| 13     | G  | GPIO 0 RW General purpose Input/Output Clock Enabl |      |        |       |     |       |      |      |    |    |    |     |      |      | abl  | e     | ſ    |      |      |      | _     |       |        |        |        |        |       |       |        |        |        |

|        | S  | et to                                              | enal | ole tł | ne cl | ock | for ( | GPIC | Э.   |    |    |    |     |      |      |      |       |      |      |      |      |       |       |        |        |        |        | J     |       |        |        |        |

- New #define for pointer to get access to CMU register -> enabling

- #define CMU\_ HFPERCLKDIV (\*(volatile unsigned long int\*)(0x400c8000 + 0x008))

- Note: CMU\_BASE\_ADDR+ CMU\_HFPERCLKDIV\_OFFS

- #define CMU\_HFPERCLKEN0 (\*(volatile unsigned long int\*)(0x400c8000 + 0x044))

- Note: CMU\_BASE\_ADDR+CMU\_HFPERCLKEN0\_OFFS

- In the main function: CMU\_HFPERCLKDIV |= (1<<8); CMU\_HFPERCLKENO |= (1<<13);</p>

- Comment out all #include not to cause any trouble

© BME-MIT

Check for errors by compiling

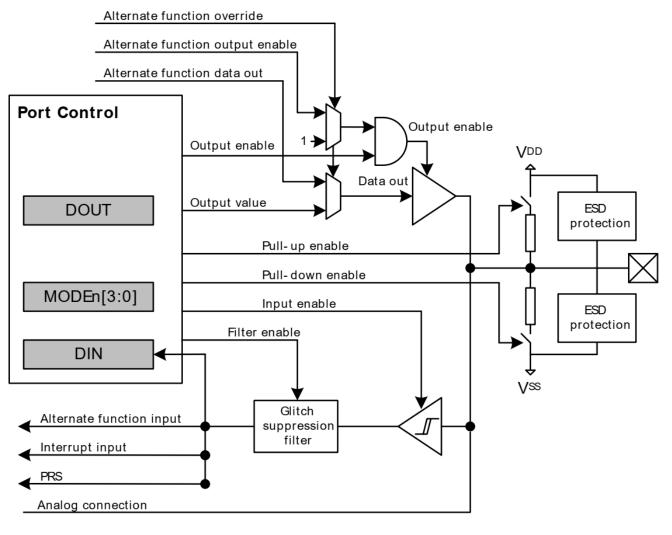

#### See pp.756-758 and Fig. 32.1 of EFM32GG-RM.pdf

© BME-MIT

Méréstechnika és Információs Rendszerek Tanszék

#### Register map of GPIO (see p.764): offsets only!

| Offset | Name          |                          | Туре | Description                 |

|--------|---------------|--------------------------|------|-----------------------------|

| 0x02C  | GPIO_PB_MODEH | Register for push button | RW   | Port Pin Mode High Register |

| 0x040  | GPIO_PB_DIN   | Register for push button | R    | Port Data In Register       |

| 0x094  | GPIO_PE_MODEL | Register for push LED    | RW   | Port Pin Mode Low Register  |

| 0x09C  | GPIO_PE_DOUT  | Register for LED         | RW   | Port Data Out Register      |

#### Use #define again

- o #define GPIO\_PB\_MODEH\_OFFS 0x02C

- o #define GPIO\_PB\_DIN\_OFFS 0x040

- o #define GPIO\_PE\_MODEL\_OFFS 0x094

- o #define GPIO\_PE\_DOUT\_OFFS 0x09C

- Pointers to be used have to be created in the same way as in case of CMU

- #define GPIO\_PB\_MODEH (\*(volatile long unsigned int \*)(GPIO\_BASE\_ADDR+GPIO\_PB\_MODEH\_OFFS))

- o #define GPIO\_PB\_DIN (\*(volatile ...\*)(...+..\_OFFS))

- o #define GPIO\_PE\_MODEL (\*(...

- o #define GPIO\_PE\_DOUT (\*(...

Check pp. 765-766, the GPIO\_Px\_CTRL (port control) register: drive modes can be set

| Offset |    |    |    |    |    |    |    |    |    |    |    |    |    |   | Bit | t Po | siti | on |    |    |    |    |   |   |   | I |   |   |   |   |     |   |

|--------|----|----|----|----|----|----|----|----|----|----|----|----|----|---|-----|------|------|----|----|----|----|----|---|---|---|---|---|---|---|---|-----|---|

| 0x000  | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 9 | 17  | 16   | 15   | 4  | 13 | 12 | 11 | 10 | ი | 8 | 7 | 9 | 5 | 4 | e | 2 | -   | 0 |

| Reset  |    |    |    |    |    |    |    |    |    |    |    |    |    |   |     |      |      |    |    |    |    |    |   |   |   |   |   |   |   |   | UXU |   |

| Access |    |    |    |    |    |    |    |    |    |    |    |    |    |   |     |      |      |    |    |    |    |    |   |   |   |   |   |   |   |   | MA  |   |

| Name   |    |    |    |    |    |    |    |    |    |    |    |    |    |   |     |      |      |    |    |    |    |    |   |   |   |   |   |   |   |   |     |   |

- Bit

Name

Reset

Access

Description

31:2

Reserved

To ensure compatibility with future devices, always write bits to 0. More information in Section 2.1 (p. 3)

1:0

DRIVEMODE

0x0

RW

Drive Mode Select

- DRIVEMODE 0x0 RW Drive Mode Sel

Select drive mode for all pins on port configured with alternate drive strength.

| Value | Mode     | Description          |

|-------|----------|----------------------|

| 0     | STANDARD | 6 mA drive current   |

| 1     | LOWEST   | 0.1 mA drive current |

| 2     | HIGH     | 20 mA drive current  |

| 3     | LOW      | 1 mA drive current   |

Méréstechnika és Információs Rendszerek Tanszék

### 8) Peripheral handling in general- GPIO

#### Check pp. 766, the GPIO\_Px\_MODEL register

| Offset |                      |                                                                                  | Bit Po               | sition               |         |       |         |

|--------|----------------------|----------------------------------------------------------------------------------|----------------------|----------------------|---------|-------|---------|

| 0x004  | 31<br>30<br>28<br>29 | 27<br>26<br>25<br>25<br>24<br>24<br>23<br>23<br>23<br>23<br>22<br>22<br>22<br>22 | 19<br>18<br>17<br>16 | 15<br>14<br>13<br>12 | 11 10 8 | 6 4 4 | 0 7 5 3 |

| Reset  | 0×0                  | 0×0                                                                              | 0×0                  | 0×0                  | 0×0     | 0×0   | 0×0     |

| Access | RW                   | RW<br>RW                                                                         | RW                   | RW                   | RW      | RW    | RW      |

| Name   | MODE7                | MODE6                                                                            | MODE4                | MODE3                | MODE2   | MODE1 | MODE0   |

|   | Bit   | Na  | me                      | Reset         |         | Access            | Description          |                  |

|---|-------|-----|-------------------------|---------------|---------|-------------------|----------------------|------------------|

|   | 31:28 | МО  | DE7                     | 0x0           |         | RW                | Pin 7 Mode           |                  |

|   |       | Cor | nfigure mode for pin 7. | Enumeration i | s equal | to MODE0.         |                      |                  |

| V | alue  |     | Mode                    |               | Descrip | otion 4bits->     | 16 different r       | nodes            |

| 0 |       |     | DISABLED                |               | Input d | isabled. Pullup i | f DOUT is set.       |                  |

| 1 |       |     | INPUT                   |               | Input e | nabled. Filter if | DOUT is set          |                  |

| 2 |       |     | INPUTPULL               |               | Input e | nabled. DOUT o    | letermines pull dire | ection           |

| 3 |       |     | INPUTPULLFILTER         |               | Input e | nabled with filte | r. DOUT determine    | s pull direction |

| 4 |       |     | PUSHPULL                |               | Push-p  | ull output        |                      |                  |

|   |       |     | 1                       |               | 1       |                   |                      |                  |

éstechnika és rmációs Rendszerek

### 8) Peripheral handling push button- GPIO

#### Check pp. 767, the GPIO Px MODEH register

| Offset |       |        |    |    |    |        |    |    |    |      |        |    |    |    | Bi     | t Po | siti | on     |    |    |   |         |   |    |   |   |        |   |       |   |   |   |  |

|--------|-------|--------|----|----|----|--------|----|----|----|------|--------|----|----|----|--------|------|------|--------|----|----|---|---------|---|----|---|---|--------|---|-------|---|---|---|--|

| 0x008  | 31    | 30     | 29 | 28 | 27 | 26     | 25 | 24 | 23 | 22   | 21     | 20 | 19 | 18 | 17     | 16   | 15   | 14     | 13 | 12 | 7 | 10      | 6 | 80 | 7 | 9 | 5      | 4 | ю     | 2 | - | 0 |  |

| Reset  | 0×0   |        |    |    |    |        |    |    |    | 0×0  |        |    |    |    |        |      |      | 0x0    |    |    |   |         |   |    |   |   | nxn    |   | 0×0   |   |   |   |  |

| Access | RW RW |        |    |    |    |        |    |    |    | 1010 |        |    |    |    | RW     |      |      | RW     |    |    |   | Md      |   |    |   |   | N<br>Y |   | RV    |   |   |   |  |

| Name   |       | 313000 |    |    |    | MODE14 |    |    |    |      | MOUEIS |    |    |    | MODE12 |      |      | MODE11 |    |    |   | MODE 10 |   |    |   |   | MODES  |   | MODE8 |   |   |   |  |

| 11:8 | MODE10            | 0x0                     | RW             | Pin 10 Mode |

|------|-------------------|-------------------------|----------------|-------------|

|      | Configure mode fo | r pin 10. Enumeration i | s equal to MOD | E8.         |

| 7:4  | MODE9             | 0x0                     | RW             | Pin 9 Mode  |

Push buttons are conncted to pins 9 and 10 -> GPIO\_Px\_MODEH should be used

Note: the MODEs are the same as before

### 8) Peripheral handling push button - GPIO

#### Push button

- Pins has to be set as inputs

- Use MODEH register of port B

- After CLK enable, use GPIO\_PB\_MODEH |= ?

- Pin 9 (10) can be configured by bit group [7:4] [11:8]

INPUT -> value is 1

|   | Value | Mode            | Description                                               |

|---|-------|-----------------|-----------------------------------------------------------|

|   | 0     | DISABLED        | Input disabled. Pullup if DOUT is set.                    |

| ſ | 1     | INPUT           | Input enabled. Filter if DOUT is set                      |

|   | 2     | INPUTPULL       | Input enabled. DOUT determines pull direction             |

|   | 3     | INPUTPULLFILTER | Input enabled with filter. DOUT determines pull direction |

|   | 4     | PUSHPULL        | Push-pull output                                          |

|   |       |                 |                                                           |

O Use GPIO\_PB\_MODEH = (1<<4); //PB9 conf as input</p>

Use GPIO\_PB\_MODEH|=(1<<8); //PB10 conf as input</li>

© BME-MIT

éstechnika és rmációs Rendszerek szék

#### Check pp. 767, the GPIO\_Px\_MODEL register

| Offset |    |    |      |    |    |    |        |    |     |    |       |    |    |    | Bi    | t Po | siti | on    |    |    |   |     |       |    |   |   |       |   |   |   |       |   |

|--------|----|----|------|----|----|----|--------|----|-----|----|-------|----|----|----|-------|------|------|-------|----|----|---|-----|-------|----|---|---|-------|---|---|---|-------|---|

| 0x004  | 31 | 30 | 29   | 28 | 27 | 26 | 25     | 24 | 23  | 22 | 21    | 20 | 19 | 18 | 17    | 16   | 15   | 14    | 13 | 12 | 7 | 10  | 6     | 8  | 2 | 9 | 5     | 4 | e | ~ | -     | 0 |

| Reset  |    |    | nxn  |    |    | 6  | nxn    |    | 0×0 |    |       |    |    |    | 0×0   |      |      | 0×0   |    |    |   | 020 | nxn   |    |   |   | 0×0   |   |   | ç | nxn   |   |

| Access |    |    |      |    |    |    | Х<br>Х |    | RŴ  |    |       |    | RŴ |    |       |      |      | RW    |    |    |   |     |       | RW |   |   | RW    |   |   |   |       |   |

| Name   |    |    | MODE |    |    |    | MODE6  |    |     |    | MUDES |    |    |    | MODE4 |      |      | MODE3 |    |    |   |     | MUDEZ |    |   |   | MODE1 |   |   |   | MODEO |   |

15:12MODE30x0RWPin 3 ModeConfigure mode for pin 3. Enumeration is equal to MODE0.11:8MODE20x0RWPin 2 Mode

Configure mode for pin 2. Enumeration is equal to MODE0.

LEDs are conncted to pins 2 and 3 -> GPIO\_Px\_MODEL should be used

#### Note: the MODEs are the same as before

#### LEDs

Pins has to be set as outputs: pin 2 and 3 in Port E

Use MODEL reg of port E

After CLK enable, use GPIO\_PE\_MODEL |= ?

• Pin 2 (3) can be configured by bit group [11:8] [15:12]

Pushpull mode has to be used whose value is a 4

| Value | Mode            | Description                                               |

|-------|-----------------|-----------------------------------------------------------|

| 0     | DISABLED        | Input disabled. Pullup if DOUT is set.                    |

| 1     | INPUT           | Input enabled. Filter if DOUT is set                      |

| 2     | INPUTPULL       | Input enabled. DOUT determines pull direction             |

| 3     | INPUTPULLFILTER | Input enabled with filter. DOUT determines pull direction |

| 4     | PUSHPULL        | Push-pull output                                          |

Use GPIO\_PE\_MODEL |= (4<<8); //PE2 conf as output</li>

O Use GPIO\_PE\_MODEL |= (4<<12); //PE3 conf as output</p>

- LEDs' default value should be set

- Check p.768

- GPIO\_Px\_DOUT

- Data output on port

- GPIO\_Px\_DOUTSET

- Write bits to 1 to set corresponding bits in GPIO\_Px\_DOUT. Bits written to 0 will have no effect.

- GPIO\_Px\_DOUTCLR

- Write bits to 1 to clear corresponding bits in GPIO\_Px\_DOUT. Bits written to 0 will have no effect.

- O GPIO\_PE\_DOUT|=(1<<2); //LED0 set</pre>

- O GPIO\_PE\_DOUT|=(1<<3); //LED1 set</pre>

### 9) Operation at a code level

- What should be written in the while loop?

- Read the status of the button (pushed/released) from the corresponding register bit and control the LED based on button state (on/off)

```

while (1) {

if (GPIO_PB_DIN & (1<<9)){

GPIO_PE_DOUT &= ~(1 << 3);

} else {

GPIO_PE_DOUT |= 1 << 3;

}

if (GPIO_PB_DIN & (1<<10)){

GPIO_PE_DOUT &= ~(1 << 2);

} else {

GPIO_PE_DOUT |= 1 << 2;

}

}</pre>

```

}

Here it should be checked based on the schematic that what is the value of the push button when -pushed (->low) -released (->high)

© BME-MIT

### 10) Some extra

- Using GPIO\_Px\_CTRL register the drive strength can be set to control the luminance of the LED

- o Check p. 767

- 32.5.1 GPIO\_Px\_CTRL Port Control Register

| Offset |                                                                                            |    |    | -  |     | Bit Position |    |       |    |    |       |        |      |             |        |        |    |              |        |       |         |       |                      |   |     |   |   |   |   |   |           |

|--------|--------------------------------------------------------------------------------------------|----|----|----|-----|--------------|----|-------|----|----|-------|--------|------|-------------|--------|--------|----|--------------|--------|-------|---------|-------|----------------------|---|-----|---|---|---|---|---|-----------|

| 0x000  | 31                                                                                         | 30 | 29 | 28 | 27  | 26           | 25 | 24    | 23 | 22 | 21    | 20     | 19   | 18          | 17     | 16     | 15 | 4            | 13     | 12    | 7       | 10    | 6                    | 8 | ~   | 9 | 5 | 4 | e | 7 | - 0       |

| Reset  |                                                                                            |    |    |    | 1   |              |    |       |    |    |       |        |      |             |        | 1      |    |              |        |       |         |       |                      | 1 |     |   |   |   |   |   | 0×0       |

| Access | Bit Name Reset Access Description                                                          |    |    |    |     |              |    |       |    |    |       |        |      |             |        |        |    |              | RW     |       |         |       |                      |   |     |   |   |   |   |   |           |

|        | 31:2     Reserved     To ensure compatibility with future devices, always write bits to 0. |    |    |    |     |              |    |       |    |    |       |        |      |             | 0.     |        |    | DE           |        |       |         |       |                      |   |     |   |   |   |   |   |           |

| Name   |                                                                                            |    |    |    | 1:0 |              |    | RIVEI |    |    | de fo | or all |      | 0x0<br>s on | port o | config |    | RW<br>d with | n alte | erna  |         |       | <b>lode</b><br>treng |   | ect |   |   |   |   |   | DRIVEMODE |

|        | _                                                                                          |    |    |    |     |              | Va | alue  |    |    | N     | lode   |      |             |        |        |    |              |        | Desc  | riptior | ı     |                      |   |     |   |   |   |   |   |           |

|        |                                                                                            |    |    |    |     |              | 0  |       |    |    | S     | TAN    | DARI | D           |        |        |    |              |        | 6 mA  | drive   | curre | ent                  |   |     |   |   |   |   |   |           |

|        |                                                                                            |    |    |    |     |              | 1  |       |    |    | L     | OWE    | ST   |             |        |        |    |              | 0      | 0.1 m | nA driv | ve cu | rrent                |   |     |   |   |   |   |   |           |

|        |                                                                                            |    |    |    |     |              | 2  |       |    |    | Н     | IGH    |      |             |        |        |    |              | :      | 20 m  | A driv  | e cur | rent                 |   |     |   |   |   |   |   |           |

|        |                                                                                            |    |    |    |     |              | 3  |       |    |    | L     | OW     |      |             |        |        |    |              |        | 1 mA  | drive   | curre | ent                  |   |     |   |   |   |   |   |           |

### 11) Reference code

//#include "em\_device.h"

//#include "em\_chip.h"

#define CMU\_BASE\_ADDR 0x400c8000 #define GPIO\_BASE\_ADDR 0x40006000

#define CMU\_HFPERCLKDIV (\*(volatile unsigned long int\*)(0x400c8000 + 0x008))

#define CMU\_HFPERCLKEN0 (\*(volatile unsigned long int\*)(0x400c8000 + 0x044))

#define GPIO\_PB\_MODEH (\*(volatile unsigned long int\*)(0x40006000 + 0x02C))

#define GPIO\_PB\_DIN (\*(volatile unsigned long int\*)(0x40006000 + 0x040))

#define GPIO\_PE\_MODEL (\*(volatile unsigned long int\*)(0x40006000 + 0x094))

#define GPIO\_PE\_DOUT (\*(volatile unsigned long int\*)(0x40006000 + 0x09C))

```

int main(void)

{

/* Chip errata */

//CHIP_Init();

CMU_HFPERCLKDIV |= 1 << 8; // periferal clk enable

CMU_HFPERCLKEN0 |= 1 << 13; // GPIO clk enable</pre>

```

### 11) Reference code (cont'd)

//

GPIO\_PE\_MODEL |= 4 << 8; // port E pin 2: pushpull output: page 766 GPIO\_PE\_MODEL |= 4 << 12;// port E pin 3: pushpull output

```

GPIO_PE_DOUT |= 1 << 2; // port E pin 2: high

GPIO_PE_DOUT |= 1 << 3; // port E pin 3: high

```

```

GPIO_PB_MODEH |= 1 << 4; // port B pin 9: input: page 67

GPIO_PB_MODEH |= 1 << 8;// port B pin 10: input

```

```

/* Infinite loop */

while (1) {

```

```

GPIO_PE_DOUT |= 1 << 2;

```

}